TJA1028 Ver la hoja de datos (PDF) - NXP Semiconductors.

Número de pieza

componentes Descripción

Fabricante

TJA1028 Datasheet PDF : 24 Pages

| |||

NXP Semiconductors

TJA1028

LIN transceiver with integrated voltage regulator

7.4 Remote wake-up

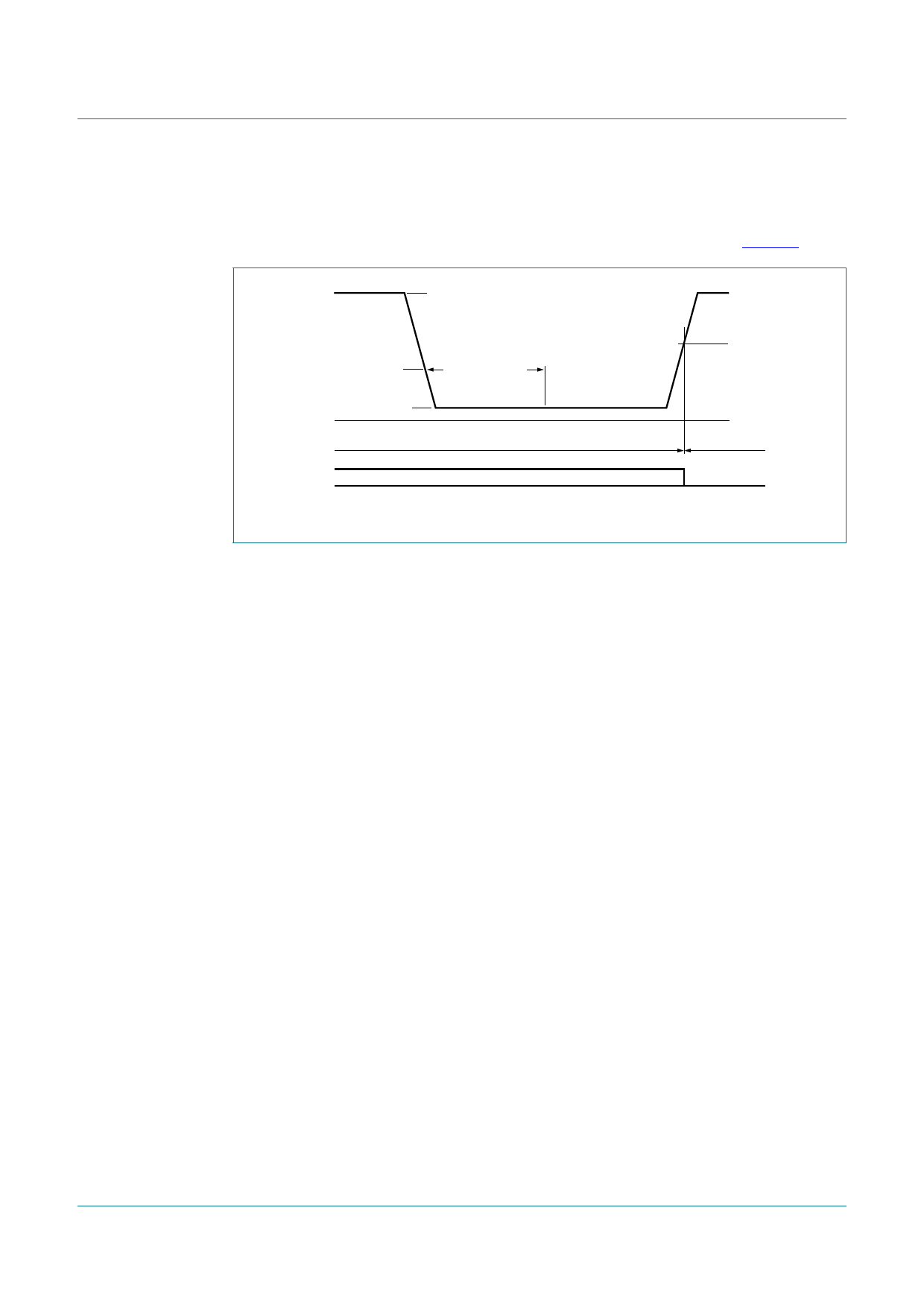

A remote wake-up is triggered by a falling edge on pin LIN, followed by LIN remaining

LOW for at least twake(busdom)min, followed by a rising edge on pin LIN (see Figure 5).

LIN recessive

VBAT

VLIN

0.4VBAT

twake(busdom)min

0.6VBAT

LIN dominant

Standby/Sleep mode

ground

Standby mode

RXD

Sleep: floating/Standby: HIGH

Fig 5. Remote wake-up behavior

LOW

015aaa088

The remote wake-up request is communicated to the microcontroller in Standby mode by

a continuous LOW level on pin RXD.

Note that twake(busdom)min is measured in Sleep and Standby modes, and in Normal mode if

TXD is HIGH.

7.5 Fail-safe features

7.5.1 General fail-safe features

The following general fail-safe features have been implemented:

• An internal pull-up towards VCC on pin TXD guarantees a recessive bus level if the pin

is left floating by a bad solder joint or floating microcontroller port pin.

• The current in the transmitter output stage is limited in order to protect the transmitter

against short circuits to pin VBAT.

• A loss of power (pins VBAT and GND) has no impact on the bus line or on the

microcontroller. There will be no reverse currents from the bus.

• The LIN transmitter is automatically disabled when either EN or RSTN is LOW.

• After a transition to Normal mode, the LIN transmitter is only enabled if a recessive

level is present on pin TXD.

7.5.2 TXD dominant time-out function

A TXD dominant time-out timer circuit prevents the bus line being driven to a permanent

dominant state (blocking all network communications) if TXD is forced permanently LOW

by a hardware or software application failure. The timer is triggered by a negative edge on

the TXD pin. If the pin remains LOW for longer than the TXD dominant time-out time

(tto(dom)TXD), the transmitter is disabled, driving the bus line to a recessive state. The timer

is reset by a positive edge on TXD.

TJA1028

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 25 February 2011

© NXP B.V. 2011. All rights reserved.

8 of 24