28F004BE Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

28F004BE Datasheet PDF : 57 Pages

| |||

4-MBIT SmartVoltage BOOT BLOCK FAMILY

E

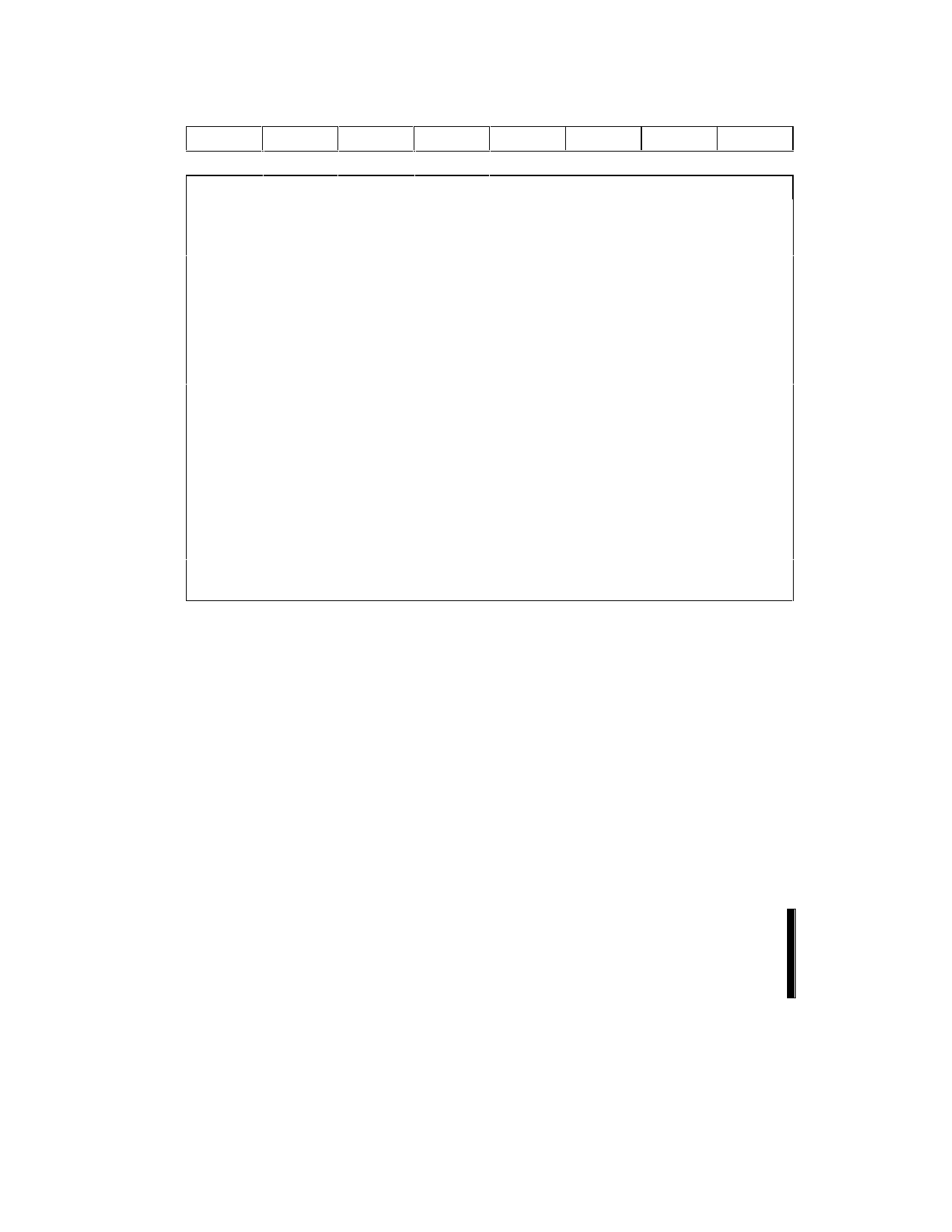

Table 8. Status Register Bit Definition

WSMS

ESS

ES

DWS

VPPS

R

R

R

7

6

5

4

3

2

1

0

NOTES:

SR.7 =WRITE STATE MACHINE STATUS

1 = Ready

(WSMS)

0 = Busy

Check Write State Machine bit first to determine

Word/Byte program or Block Erase completion,

before checking Program or Erase Status bits.

SR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase In Progress/Completed

When Erase Suspend is issued, WSM halts

execution and sets both WSMS and ESS bits to

“1.” ESS bit remains set to “1” until an Erase

Resume command is issued.

SR.5 = ERASE STATUS (ES)

1 = Error In Block Erasure

0 = Successful Block Erase

When this bit is set to “1,” WSM has applied the

max number of erase pulses to the block and is

still unable to verify successful block erasure.

SR.4 = PROGRAM STATUS (DWS)

1 = Error in Byte/Word Program

0 = Successful Byte/Word Program

When this bit is set to “1,” WSM has attempted

but failed to program a byte or word.

SR.3 = VPP STATUS (VPPS)

1 = VPP Low Detect, Operation Abort

0 = VPP OK

The VPP Status bit does not provide continuous

indication of VPP level. The WSM interrogates VPP

level only after the Byte Write or Erase command

sequences have been entered, and informs the

system if VPP has not been switched on. The VPP

Status bit is not guaranteed to report accurate

feedback between VPPLK and VPPH.

SR.2-SR.0 = RESERVED FOR FUTURE

ENHANCEMENTS (R)

These bits are reserved for future use and should

be masked out when polling the Status Register.

3.3.2

STATUS REGISTER

The device Status Register indicates when a

program or erase operation is complete, and the

success or failure of that operation. To read the

Status Register write the Read Status (70H)

command to the CUI. This causes all subsequent

read operations to output data from the Status

Register until another command is written to the

CUI. To return to reading from the array, issue a

Read Array (FFH) command.

The Status Register bits are output on DQ0–DQ7, in

both byte-wide (x8) or word-wide (x16) mode. In the

word-wide mode the upper byte, DQ8–DQ15,

outputs 00H during a Read Status command. In the

byte-wide mode, DQ8–DQ14 are tri-stated and

DQ15/A–1 retains the low order address function.

Important: The contents of the Status Register

are latched on the falling edge of OE# or CE#,

whichever occurs last in the read cycle. This

prevents possible bus errors which might occur if

Status Register contents change while being read.

CE# or OE# must be toggled with each subsequent

status read, or the Status Register will not indicate

completion of a program or erase operation.

When the WSM is active, the SR.7 register will

indicate the status of the WSM, and will also hold

the bits indicating whether or not the WSM was

successful in performing the desired operation.

20

PRELIMINARY