80C196NP Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

80C196NP Datasheet PDF : 51 Pages

| |||

8XC196NP COMMERCIAL CHMOS 16-BIT MICROCONTROLLER

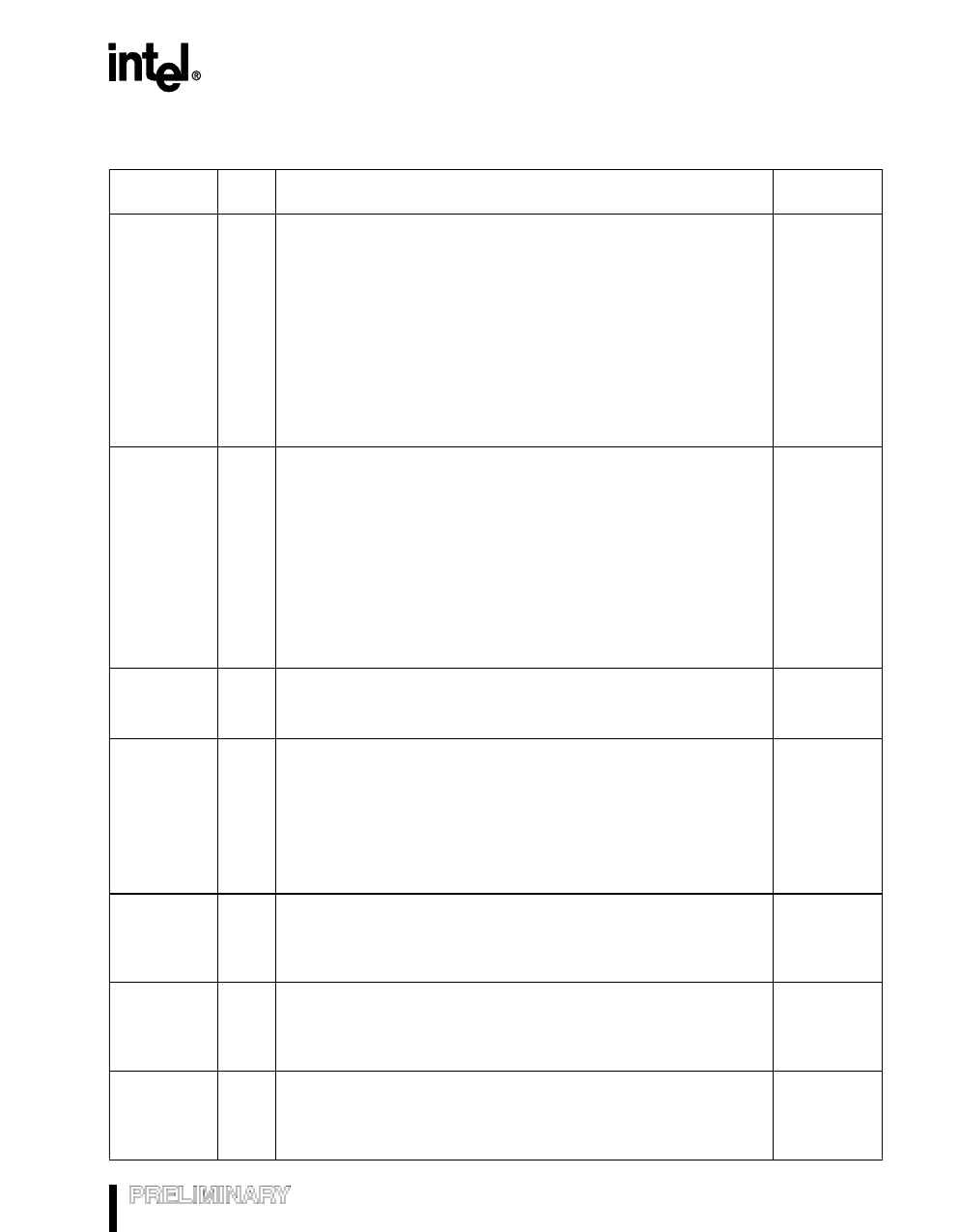

Name

RESET#

RPD

RXD

T1CLK

T2CLK

T1DIR

T2DIR

Table 8. Pin Descriptions (Continued)

Type

Description

Multiplexed

with

I/O Reset

—

A level-sensitive reset input to and open-drain system reset output

from the microcontroller. Either a falling edge on RESET# or an

internal reset turns on a pull-down transistor connected to the

RESET# pin for 16 state times. In the powerdown, standby, and idle

modes, asserting RESET# causes the chip to reset and return to

normal operating mode. After a device reset, the first instruction

fetch is from FF2080H (or F2080H in external memory). For the

80C196NP, the program and special-purpose memory locations

(FF2000–FF2FFFH) reside in external memory. For the 83C196NP,

these locations can reside either in external memory or in internal

ROM.

I Return from Powerdown

—

Timing pin for the return-from-powerdown circuit.

If your application uses powerdown mode, connect a capacitor

between RPD and VSS if the internal oscillator is the clock source.

The capacitor causes a delay that enables the oscillator to stabilize

before the internal CPU and peripheral clocks are enabled.

The capacitor is not required if your application uses powerdown

mode and if an external clock input is the clock source.

If your application does not use powerdown mode, leave this pin

unconnected.

I/O Receive Serial Data

P2.1

In modes 1, 2, and 3, RXD receives serial port input data. In mode

0, it functions as either an input or an open-drain output for data.

I Timer 1 External Clock

P1.4

External clock for timer 1. Timer 1 increments (or decrements) on

both rising and falling edges of T1CLK. Also used in conjunction

with T1DIR for quadrature counting mode.

and

External clock for the serial I/O baud-rate generator input (program

selectable).

I Timer 2 External Clock

P1.6

External clock for timer 2. Timer 2 increments (or decrements) on

both rising and falling edges of T2CLK. Also used in conjunction

with T2DIR for quadrature counting mode.

I Timer 1 External Direction

P1.5

External direction (up/down) for timer 1. Timer 1 increments when

T1DIR is high and decrements when it is low. Also used in

conjunction with T1CLK for quadrature counting mode.

I Timer 2 External Direction

P1.7

External direction (up/down) for timer 2. Timer 2 increments when

T2DIR is high and decrements when it is low. Also used in

conjunction with T2CLK for quadrature counting mode.

15