LC89170M Ver la hoja de datos (PDF) - SANYO -> Panasonic

Número de pieza

componentes Descripción

Fabricante

LC89170M Datasheet PDF : 8 Pages

| |||

LC89170M

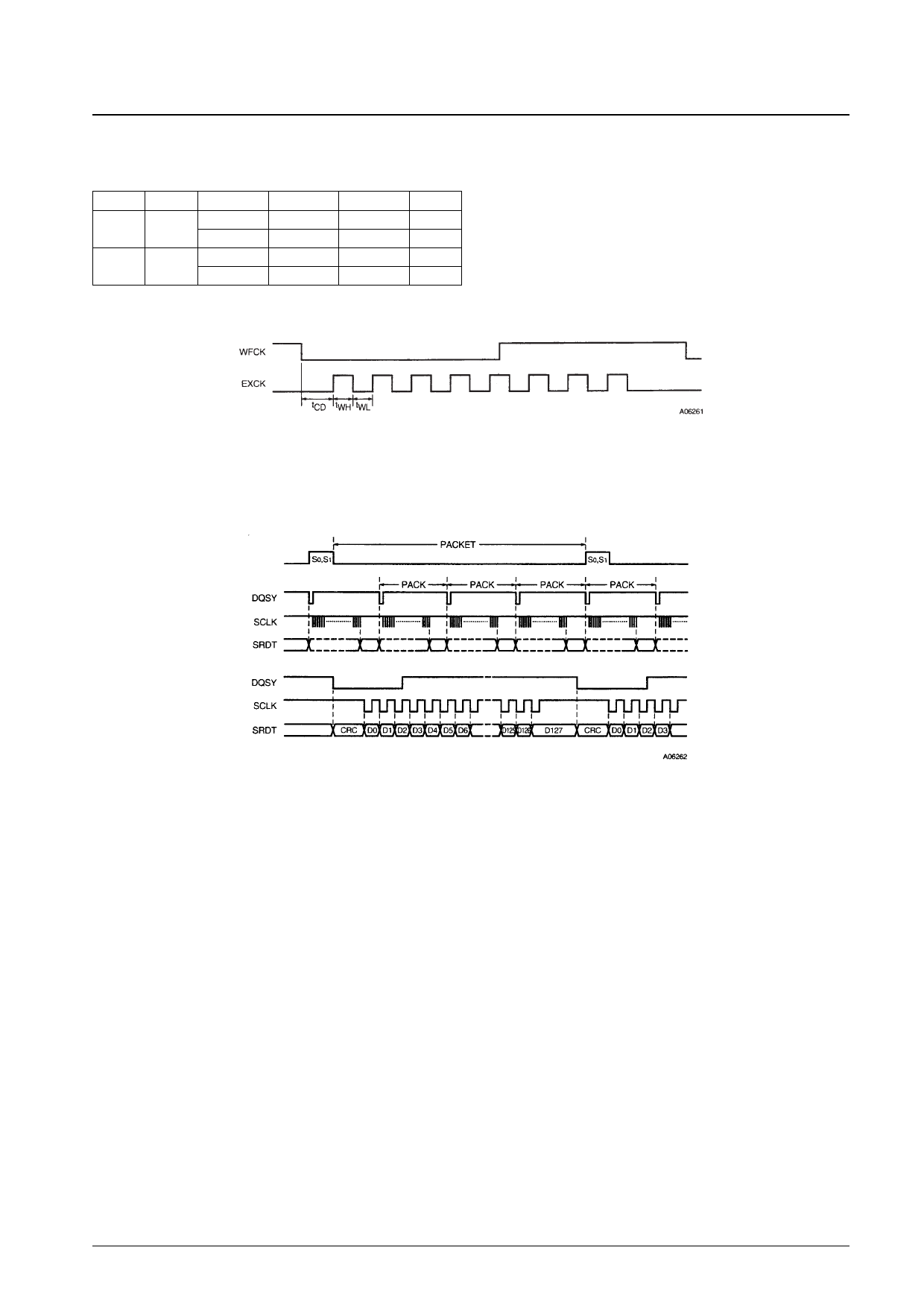

The EXCK clock characteristics are determined by SW2 as listed in the table below.

EXCK Clock Selection by SW2

SW1

SW2

tCD

tWH

tWL

Unit

12.28

1.89

1.89

µs

[L]

[L]

208TMCK

32TMCK

32TMCK

µs

18.90

7.56

7.56

µs

[L]

[H]

320TMCK

128TMCK

128TMCK

µs

The upper boxes assume MCK = 16.934 MHz

The lower boxes indicate the relationship with MCK (TMCK = 1/MCK)

• Microcontroller interface

The LC89170M includes a 32-word × 8-bit dual-port RAM on chip, and the 1PACK 24 symbols from subcode channels

R to W can be read out once every 3.3 ms (or once every 1.66 for double-speed playback) over the microcontroller

interface. Figure 3 shows the timing.

Figure 3 Microcontroller Interface Output Timing

The 1PACK 24 symbols for the subcode R to W data (18 bytes) are entered into the dual-port RAM and input to the CRC

checking circuit. After the data for 1 PACK has all been input, a falling edge is output from the DQSY pin and the CRC

flags are output from SRDT. A high is output for the CRC flags if the check returned OK. Next, 128 bits of data are

output by inputting the SCLK clock signal. A single packet of data is output by repeating this operation four times.

No. 5536-6/8