SY100E150(1998) Ver la hoja de datos (PDF) - Micrel

Número de pieza

componentes Descripción

Fabricante

SY100E150 Datasheet PDF : 4 Pages

| |||

6-BIT D

LATCH

SY10E150

SY100E150

FEATURES

s 700ps max. propagation delay

s Extended 100E VEE range of –4.2V to –5.5V

s Differential outputs

s Fully compatible with industry standard 10KH,

100K ECL levels

s Internal 75KΩ input pulldown resistors

s Fully compatible with Motorola MC10E/100E150

s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E150 are 6-bit D latches with differential

outputs designed for use in new, high- performance ECL

systems. When both Latch Enables (LEN1, LEN2) are at a

logic LOW, the latch is in the transparent mode and input

data propagates through to the output. A logic HIGH on

either LEN1 or LEN2 (or both) latches the input data. The

Master Reset (MR) overrides all other signals to set the Q

outputs to a logic LOW.

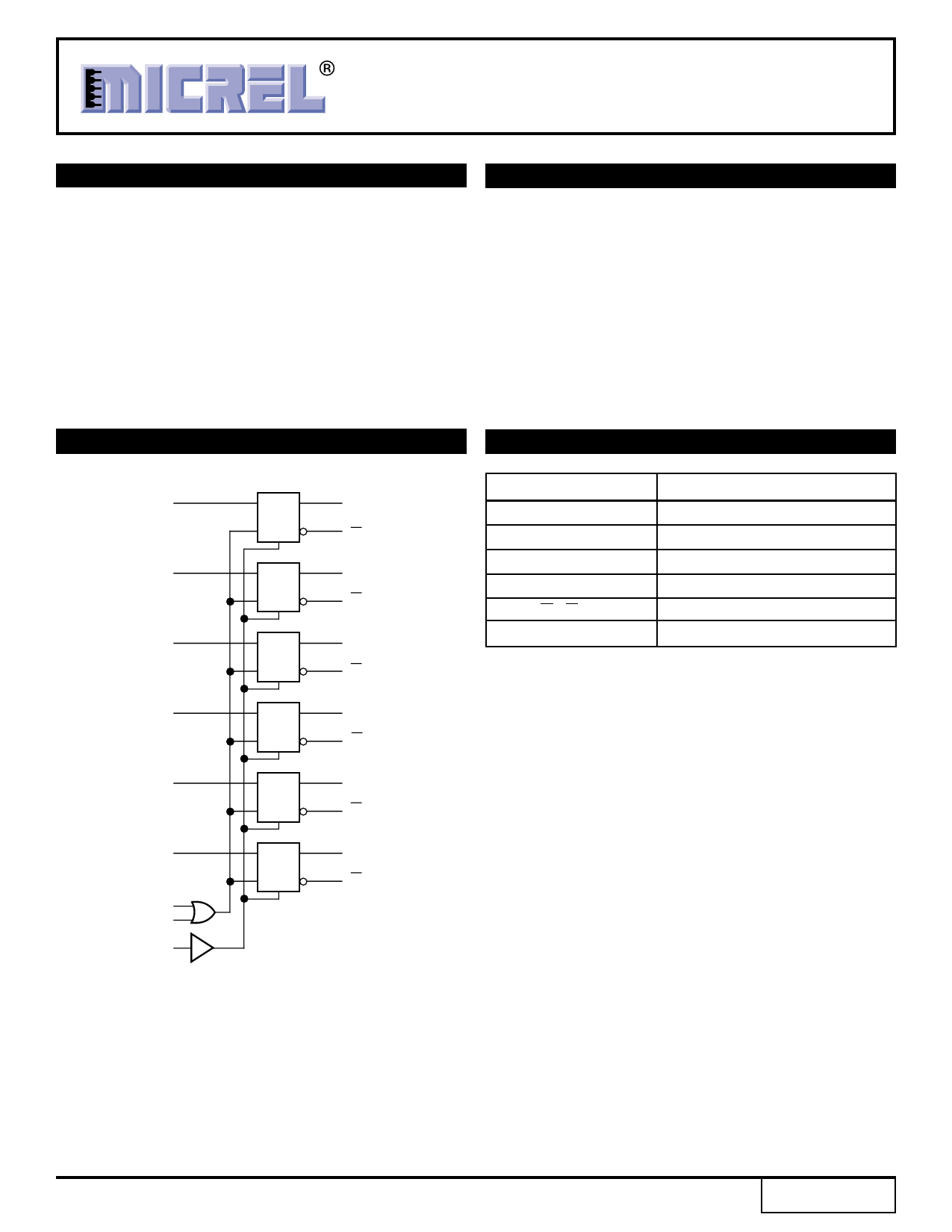

BLOCK DIAGRAM

D0

D1

D2

D3

D4

D5

LEN1

LEN2

MR

D

Q0

R

Q0

D

Q1

R

Q1

D

Q2

R

Q2

D

Q3

R

Q3

D

Q4

R

Q4

D

Q5

R

Q5

PIN CONFIGURATION

D5

D4

D3

VEE

D2

D1

D0

25 24 23 22 21 20 19

26

18

27

17

28

16

PLCC

1

TOP VIEW

15

2

J28-1

14

3

13

4

12

5 6 7 8 9 10 11

Q4

Q4

VCC

Q3

Q3

Q2

Q2

PIN NAMES

Pin

D0–D5

LEN1, LEN2

MR

Q0–Q5

Q0–Q5

VCCO

Function

Data Inputs

Latch Enables

Master Reset

True Outputs

Inverting Outputs

VCC to Output

Rev.: D

Amendment: /0

1

Issue Date: November, 1998