ST8024S Ver la hoja de datos (PDF) - Sitronix Technology Co., Ltd.

Número de pieza

componentes Descripción

Fabricante

ST8024S Datasheet PDF : 27 Pages

| |||

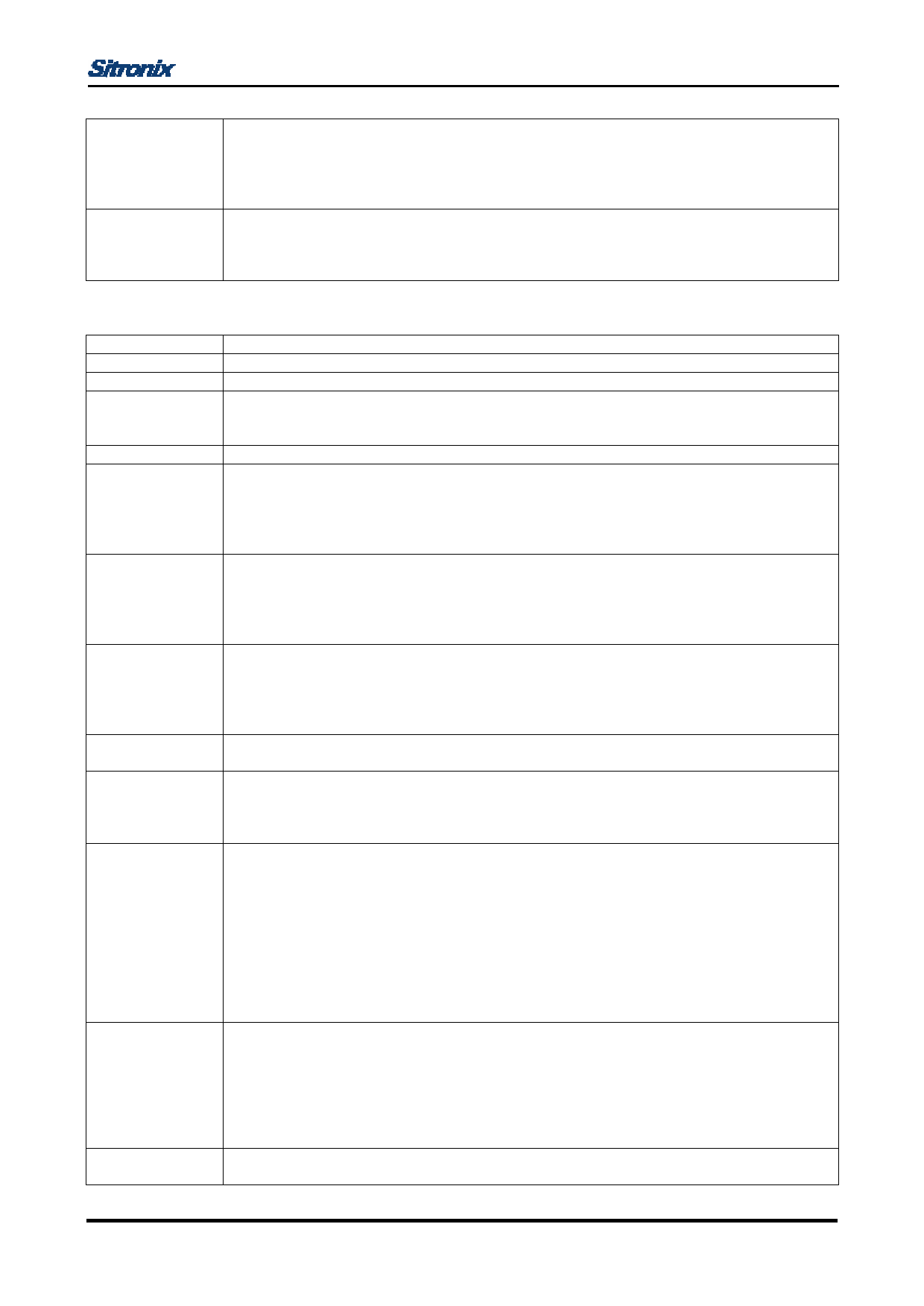

ST8024S

Y1 -Y240

read, set

to "L” for one cycle (from falling edge to failing edge of XCK), after which it returns to

"H".

Ÿ During input, the chip is selected while El is set to "L" after the LP signal is input. The

chip is non-selected after 240 bits of data have been read.

LCD drive output pins

Ÿ Corresponding directly to each bit of the data latch, one level (V0, V12, V43, or VSS) is

selected and output.

Ÿ Table of truth values is shown in "TRUTH TABLE" in Functional Operations.

(Common mode)

SYMBOL

VDD

GND

LGND

VSS

V0L, V0R

V12L, V12R

V43L, V43R

ElO1

EIO2

LP

L/R

/DISPOFF

FR

MD

FUNCTION

Logic system power supply pin, connected to +2.5 to +5.5 V.

Ground pin

Logic ground pin

Ÿ Do not short LGND with GND and Vss by ITO on LCD panel

Ÿ Connect it to GND on PCB or FPC.

Connect to GND by ITO on LCD panel.

Bias power supply pins for LCD drive voltage

Ÿ Normally use the bias voltages set by a resistor divider.

Ÿ Ensure that voltages are set such that VSS < V43 < V12 < V0.

Ÿ ViL and ViR (i = 0,12, 43) must connect to an external power supply, and supply regular

voltage which is assigned by specification for each power pin.

Shift data input/output pin for bi-directional shift register

Ÿ Output pin when L/R is at LGND level "L', input pin when L/R is at VDD level "H".

Ÿ When L/R = H, ElO1 is used as input pin, it will be pulled down.

Ÿ When L/R = L, ElO1 is used as output pin, it won't be pulled down.

Ÿ Refer to section 6.2.2.

Shift data input/output pin for bi-directional shift register

Ÿ Input pin when L/R is at LGND level "L", output pin when L/R is at VDD level "H".

Ÿ When L/R = L, EIO2 is used as input pin, it will be pulled down.

Ÿ When L/R = H, EIO2 is used as output pin, it won't be pulled down.

Ÿ Refer to section 6.2.2.

Shift clock pulse input pin for bi-directional shift register

Ÿ Data is shifted at the falling edge of the clock pulse.

Input pin for selecting the shift direction of bi-directional shift register

Ÿ Data is shifted from Y240 to Y1 when set to LGND level "L", and data is shifted from Y1 to

Y240 when set to VDD level "H".

Ÿ Refer to section 6.2.2.

Control input pin for output of non-select level

Ÿ The input signal is level-shifted from logic voltage level to LCD drive voltage level, and

controls the LCD drive circuit.

Ÿ When set to LGND level "L", the LCD drive output pins (Y1-Y240) are set to level LGND.

Ÿ When set to "L”, the contents of the shift register are reset to not reading data. When

the /DISPOFF function is canceled, the driver outputs non-select level (V12 or V43), and

the shift data is read at the next falling edge of the LP. At that time, if /DISPOFF

removal time does not correspond to what is shown in AC characteristics, the shift data

is not read correctly.

Ÿ Table of truth values is shown in "TRUTH TABLE" in Functional Operations.

AC signal input pin for LCD drive waveform

Ÿ The input signal is level-shifted from logic voltage level to LCD drive voltage level, and

controls the LCD drive circuit.

Ÿ Normally it inputs a frame inversion signal.

Ÿ The LCD drive output pins' output voltage levels can be set using the shift register

output signal and the FR signal.

Ÿ Table of truth values is shown in "TRUTH TABLE" in Functional Operations.

Mode selection pin

Ÿ When set to LGND level "L", single mode operation is selected; when set to VDD level

Ver 0.39

Page 7/27

2008/05/05