ST7032 Ver la hoja de datos (PDF) - Sitronix Technology Co., Ltd.

Número de pieza

componentes Descripción

Fabricante

ST7032 Datasheet PDF : 63 Pages

| |||

ST7032

· Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message

· Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to

do so and the message is not corrupted

· Synchronization: procedure to synchronize the clock signals of two or more devices.

ACKNOWLEDGE

Acknowledge is not Busy Flag in I2C interface.

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the

transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is

addressed must generate an acknowledge after the reception of each byte. A master receiver must also generate an

acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that

acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during

the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master

receiver must signal an end-of-data to the transmitter by not generating an acknowledge on the last byte that has been

clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP

condition. Acknowledgement on the I2C Interface is illustrated in Fig.4.

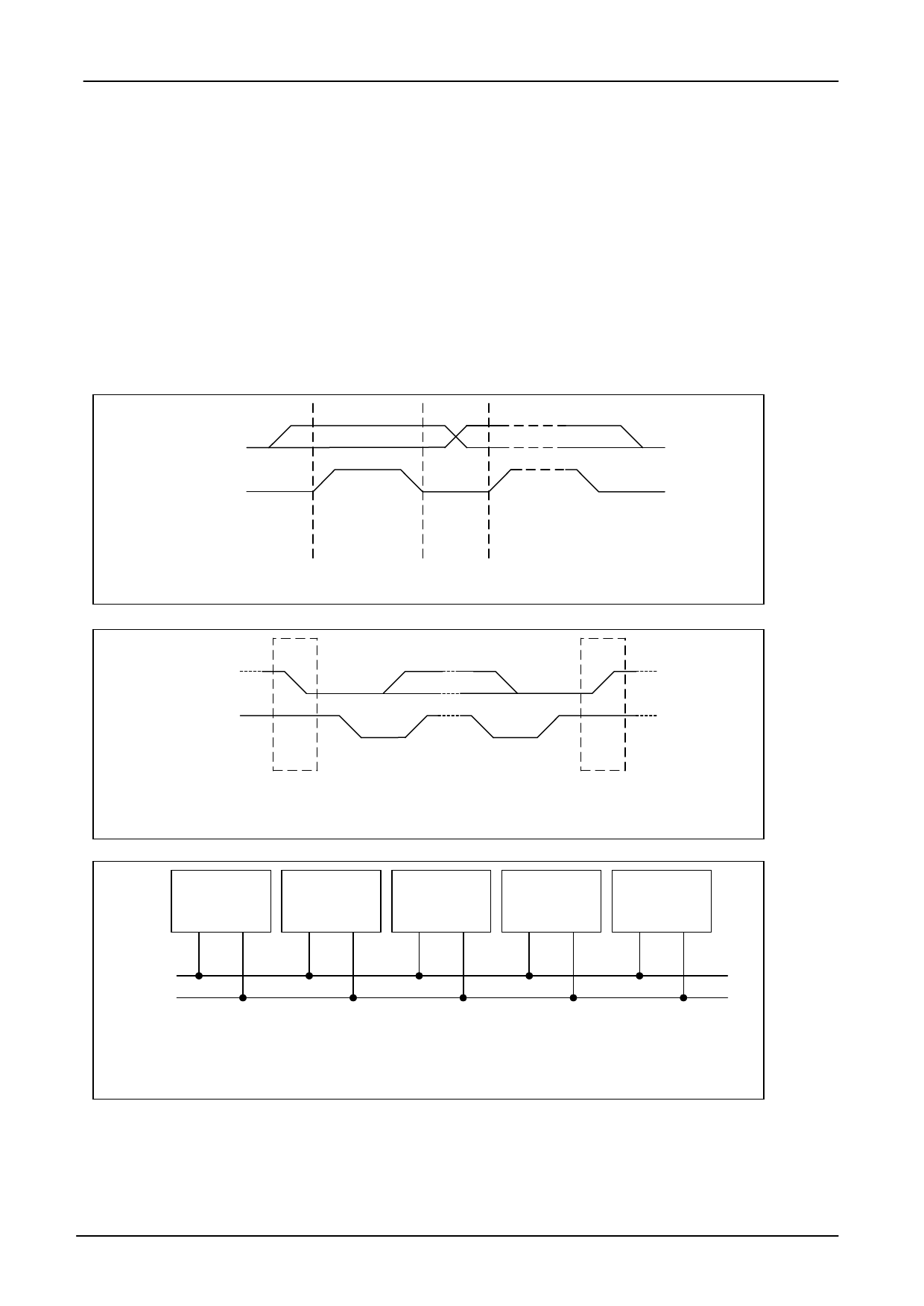

SDA

SCL

data line

stable;

data valid

change

of data

allowed

Figure 1. Bit transfer

SDA

SCL

S

P

START con dition

STOP con dition

Figure 2. Definition of START and STOP conditions

MASTER

TRANSMITTER/

RECEIVER

SLAVE

RECEIVER (1)

0111100

SLAVE

RECEIVER (2)

0111101

SLAVE

RECEIVER (3)

0111110

SLAVE

RECEIVER (4)

0111111

SDA

SCL

Figure 3. System configuration

V1.4

11/61

2008/08/18