ST70134 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

ST70134 Datasheet PDF : 8 Pages

| |||

ST70134 - ST70135A

Discrete MultiTone Digital Modem (ST70135A)

The DMT modem has been developed in

HCMOS6 (0.35µm) technology. It performs PMD

(Physycal Medium Dependant) sub-layer and TC

(Transmission Convergence) sub-layer functions.

In other words we can split the chip into two

separate blocks: the first one which carries out

modem functions (PMD sub layer) and a second

one in charge of ATM framing. The chip is

controlled and programmed by an external

processor and is seen as a memory mapped

device.

MODEM Functions

The modem part of the chip includes all the

necessary blocks needed for digitally DMT

mapping and demapping. A 14-bit code for every

carrier allows constellations with up to 16383

points. Internally, digital filters carry out Time

Equalization to reduce the effects of the inter

symbol interference. That is followed by Fast

Fourier Transform (in transmit direction an Inverse

FFT is performed) in order to change from time

domain to frequency domain. Afterwards a

Frequency Equalization cuts down carrier by

carrier the channel distortion, signal’s amplitude

attenuation and phase rotation. By efficient

algorithms, this block drives, through the

ST70134’s integrated VCXO controller, the NT

crystal oscillator which comes up in an excellent

synchronisation (less than 2ppm) with ATU-C.

FRAMING Functions

ST70135A performs framing functions for generic

and ATM TC sub layers.

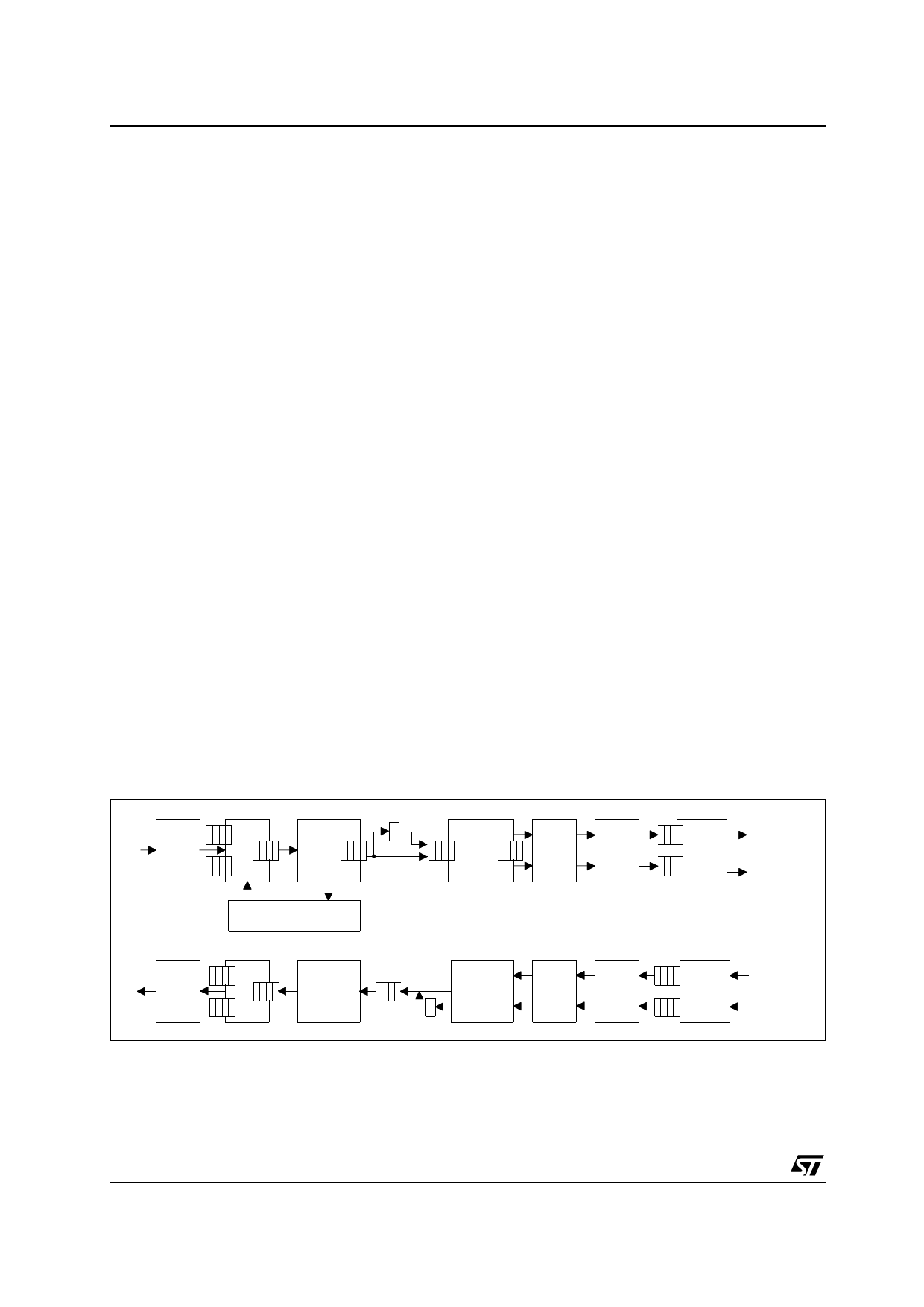

Figure 3 : DMT Modem block diagram

ATM TC sub layer performs cell level functions:

delineation, idle cells or unassigned cells

insertion/extraction, payload scrambling, Header

Error Correction (HEC) check and data frame

generation.

ST70135A DMT modem main features:

– Time-domain equalisation

– Rotor and frequency-domain equalisation

– Decimation, interpolation

– FFT and IFFT

– Mapping/demapping over 256 carriers

– Trellis coding and decoding using Viterbi algorithm

– Error and noise monitoring on individual tones

– Reed-Solomon encoding and decoding

– (De) framing and (de) interleaving

– Cell HEC generation/verification

– Payload (de) scrambling

– ATM cell insertion/extraction

– Idle &/or Unassigned cell insertion/filtering

– VPI/VCI filtering

– UTOPIA interface (Level 1 or 2)

– Microcontroller interface with 16-bit multiplexed

address/data bus and big/little endian format

supported

– JTAG test port

– Single 3.3V supply, 1.0W

– PQFP144 (28 x 28mm body, 0.65mm pitch)

Rx

DSP FE

FFT

DEMAPPER

VITERBI

ADSL

AFE

Tx

DSP FE

SIGNAL MONITORING

& FEQ UPDATE & DPLL

PMD SUBLAYER

IFFT

MAPPER

VITERBI

R/S

DECODER

DE-

FRAMER

CELL

BASED

FUNCT.

TC SUBLAYER

Rx

INTERF.

INTERLEAVED

FAST

ATM (UTOPIA)

R/S

CODER

FRAMER

CELL

BASED

FUNCT.

Tx

INTERF.

FAST

INTERLEAVED

4/8