SST25VF016B Ver la hoja de datos (PDF) - Silicon Storage Technology

Número de pieza

componentes Descripción

Fabricante

SST25VF016B Datasheet PDF : 28 Pages

| |||

Data Sheet

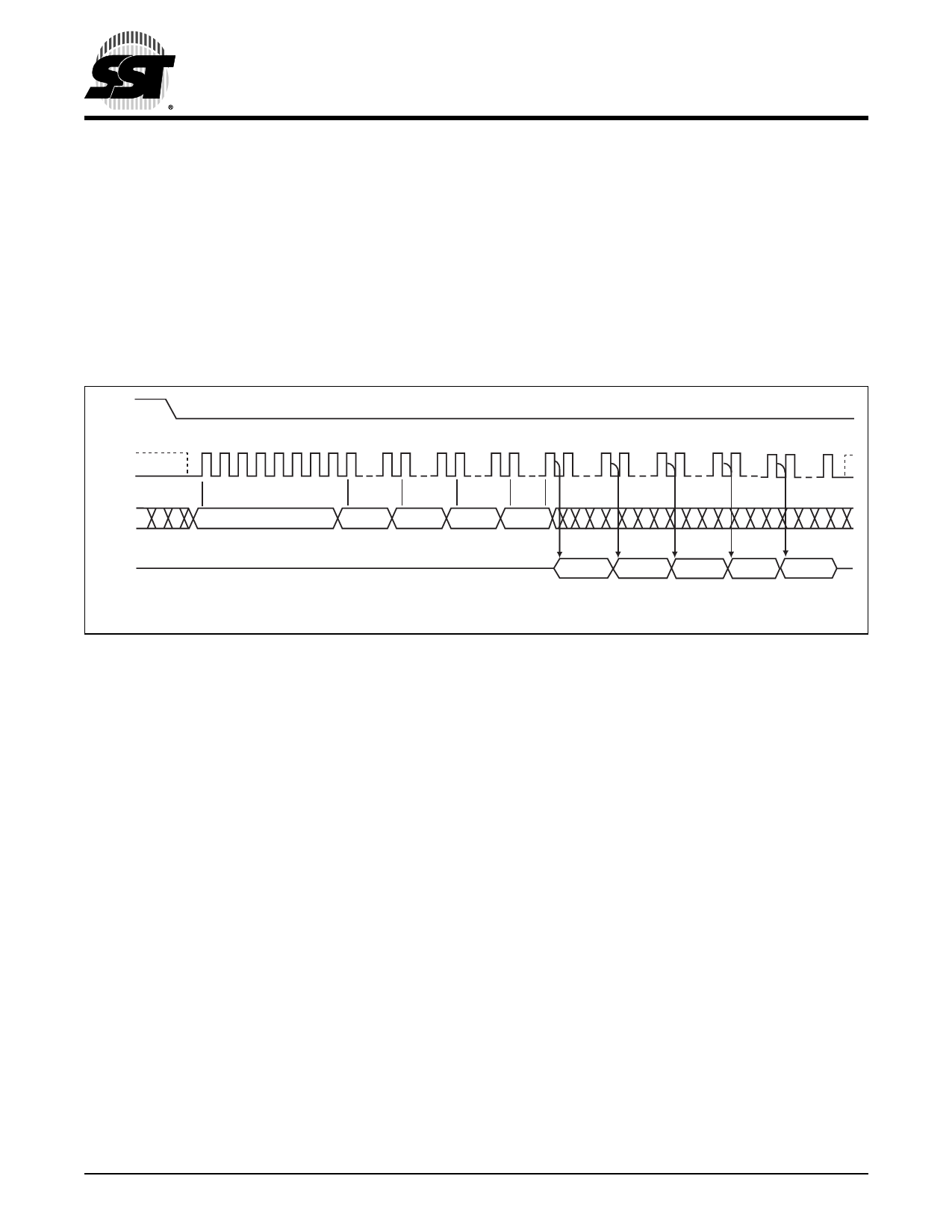

High-Speed-Read (80 MHz)

The High-Speed-Read instruction supporting up to 80 MHz

Read is initiated by executing an 8-bit command, 0BH, fol-

lowed by address bits [A23-A0] and a dummy byte. CE#

must remain active low for the duration of the High-Speed-

Read cycle. See Figure 6 for the High-Speed-Read

sequence.

Following a dummy cycle, the High-Speed-Read instruc-

tion outputs the data starting from the specified address

location. The data output stream is continuous through all

16 Mbit SPI Serial Flash

SST25VF016B

addresses until terminated by a low to high transition on

CE#. The internal address pointer will automatically incre-

ment until the highest memory address is reached. Once

the highest memory address is reached, the address

pointer will automatically increment to the beginning (wrap-

around) of the address space. Once the data from address

location 1FFFFFH has been read, the next output will be

from address location 000000H.

CE#

MODE 3 0 1 2 3 4 5 6 7 8 15 16 23 24 31 32 39 40 47 48 55 56 63 64 71 72 80

SCK MODE 0

SI

0B

ADD. ADD. ADD.

X

MSB

MSB

SO

HIGH IMPEDANCE

N

DOUT

N+1

DOUT

N+2

DOUT

N+3

DOUT

N+4

DOUT

Note: X = Dummy Byte: 8 Clocks Input Dummy Cycle (VIL or VIH)

MSB

1271 HSRdSeq.0

FIGURE 6: High-Speed-Read Sequence

©2008 Silicon Storage Technology, Inc.

10

S71271-03-000

9/08