SAA1575HL Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Fabricante

SAA1575HL Datasheet PDF : 56 Pages

| |||

Philips Semiconductors

Global Positioning System (GPS)

baseband processor

Product specification

SAA1575HL

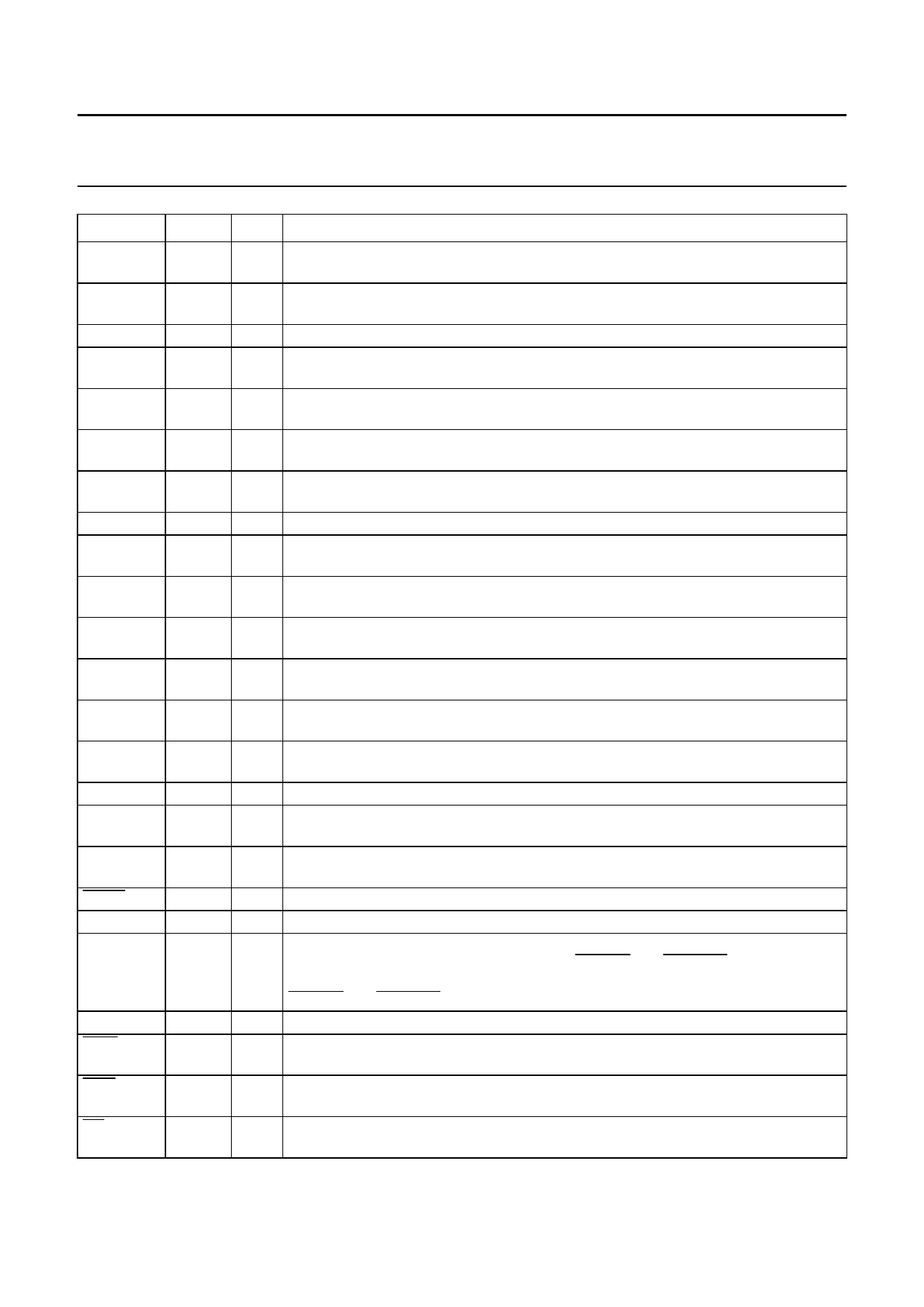

SYMBOL PIN I/O

DESCRIPTION

A11

24

O External memory address bus bit 11: 19-bit address bus; used to address external

RAM and program memory

VCC(P)

25

− Main I/O power supply: 2.7 to 5.5 V operating range; main supply for the periphery

in normal operation

VSS

26

− Ground: 0 V reference

A10

27

O External memory address bus bit 10: 19-bit address bus; used to address external

RAM and program memory

A9

28

O External memory address bus bit 9: 19-bit address bus; used to address external

RAM and program memory

A8

29

O External memory address bus bit 8: 19-bit address bus; used to address external

RAM and program memory

VCC(core)

30

− Main core power supply: 2.7 to 3.6 V only; main supply for the core in normal

operation

VSS

31

− Ground: 0 V reference

A7

32

O External memory address bus bit 7: 19-bit address bus; used to address external

RAM and program memory

A6

33

O External memory address bus bit 6: 19-bit address bus; used to address external

RAM and program memory

A5

34

O External memory address bus bit 5: 19-bit address bus; used to address external

RAM and program memory

A4

35

O External memory address bus bit 4: 19-bit address bus; used to address external

RAM and program memory

A3

VCC(P)

VSS

A2

36

O External memory address bus bit 3: 19-bit address bus; used to address external

RAM and program memory

37

− Main I/O power supply: 2.7 to 5.5 V operating range; main supply for the periphery

in normal operation

38

− Ground: 0 V reference

39

O External memory address bus bit 2: 19-bit address bus; used to address external

RAM and program memory

A1

40

O External memory address bus bit 1: 19-bit address bus; used to address external

RAM and program memory

PMCS

41

O External program memory select: external program memory read strobe

TP2

42

I Test pin: tie LOW

RSTIME

43

I Reset timer control: this controls the on-chip reset timer. If this is HIGH, reset will be

de-asserted approximately 10 ms after both PWRDN and PWRFAIL go HIGH. If this

is LOW, reset will be de-asserted approximately 10 µs after both

PWRDN and PWRFAIL go HIGH.

TP1

44

I Test pin: tie LOW

WRH

45

I/O Write MSB: write strobe for external data memory; asserted for both MSB and word

write operations; input mode only used for test purposes

WRL

46

I/O Write LSB: write strobe for external data memory; asserted for both LSB and word

write operations; input mode only used for test purposes

RD

47

I/O External data read: read strobe for external data memory; input mode only used for

test purposes

1999 Jun 04

7