MT4LC8M8C2 Ver la hoja de datos (PDF) - Micron Technology

Número de pieza

componentes Descripción

Fabricante

MT4LC8M8C2 Datasheet PDF : 22 Pages

| |||

8 MEG x 8

EDO DRAM

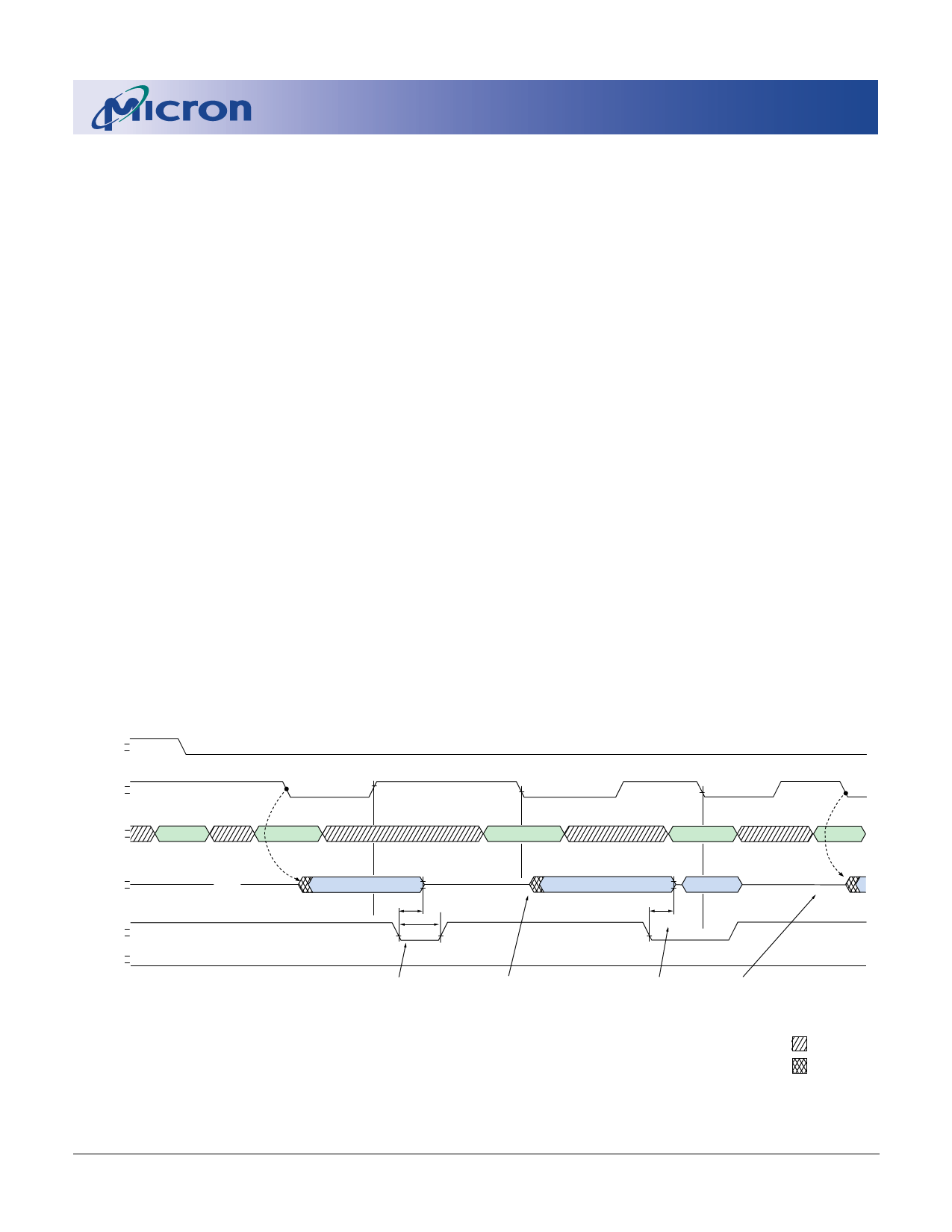

EDO PAGE MODE (continued)

other cycles, the outputs are disabled at tOFF time after

RAS# and CAS# are HIGH or at tWHZ after WE# transi-

tions LOW. The tOFF time is referenced from the rising

edge of RAS# or CAS#, whichever occurs last. WE# can

also perform the function of disabling the output

drivers under certain conditions, as shown in Figure 2.

EDO-PAGE-MODE operations are always initiated

with a row address strobed in by the RAS# signal,

followed by a column address strobed in by CAS#,

just like for single location accesses. However, subse-

quent column locations within the row may then be

accessed at the page mode cycle time. This is accom-

plished by cycling CAS# while holding RAS# LOW and

entering new column addresses with each CAS# cycle.

Returning RAS# HIGH terminates the EDO-PAGE-MODE

operation.

DRAM REFRESH

The supply voltage must be maintained at the speci-

fied levels, and the refresh requirements must be met in

order to retain stored data in the DRAM. The refresh

requirements are met by refreshing all 8,192 rows (P4)

or all 4,096 rows (C2) in the DRAM array at least once

every 64ms. The recommended procedure is to execute

4,096 CBR REFRESH cycles, either uniformly spaced or

grouped in bursts, every 64ms. The MT4LC8M8P4 in-

ternally refreshes two rows for every CBR cycle, whereas

the MT4LC8M8C2 refreshes one row for every CBR

cycle. So with either device, executing 4,096 CBR cycles

RAS#

V IH

V IL

CAS#

V IH

V IL

ADDR

V IH

V IL

ROW

COLUMN (A)

covers all rows. The CBR REFRESH cycle will invoke the

internal refresh counter for automatic RAS# address-

ing. Alternatively, RAS#-ONLY REFRESH capability is

inherently provided. However, with this method, some

compatibility issues may become apparent. For ex-

ample, both C2 and P4 versions require 4,096 CBR

REFRESH cycles, yet each requires a different number of

RAS#-ONLY REFRESH cycles (C2 = 4,096 and P4 =

8,192). JEDEC strongly recommends the use of CBR

REFRESH for this device.

An optional self refresh mode is also available on the

“S” version. The self refresh feature is initiated by

performing a CBR REFRESH cycle and holding RAS#

LOW for the specified tRASS. The “S” option allows for

an extended period of 128ms, or 31.25µs per row for a

4K refresh and 15.625µs per row for an 8K refresh, when

using a distributed CBR REFRESH. This refresh rate can

be applied during normal operation, as well as during

a standby or battery backup mode.

The self refresh mode is terminated by driving RAS#

HIGH for a minimum time of tRPS. This delay allows for

the completion of any internal refresh cycles that may

be in process at the time of the RAS# LOW-to-HIGH

transition. If the DRAM controller uses a distributed

CBR refresh sequence, a burst refresh is not required

upon exiting self refresh. However, if the DRAM

controller utilizes a RAS#-ONLY or burst CBR refresh

sequence, all 1,024 rows must be refreshed using a

minimum tRC refresh rate prior to resuming normal

operation.

COLUMN (B)

COLUMN (C)

COLUMN (D)

DQ

V IOH

V IOL

WE#

V IH

V IL

OE#

V

V

IH

IL

OPEN

VALID DATA (A)

tWHZ

tWPZ

VALID DATA (B)

tWHZ

INPUT DATA (C)

The DQs go to High-Z if WE# falls and, if tWPZ is met,

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

Figure 2

WE# CONTROL of DQs

WE# may be used to disable the DQs to prepare

for input data in an EARLY WRITE cycle. The DQs

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

DON’T CARE

UNDEFINED

8 Meg x 8 EDO DRAM

D20_2.p65 – Rev. 5/00

4

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2000, Micron Technology, Inc.