PCF2119VU-2 Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Fabricante

PCF2119VU-2 Datasheet PDF : 68 Pages

| |||

Philips Semiconductors

LCD controllers/drivers

Product specification

PCF2119X

7 FUNCTIONAL DESCRIPTION

7.1 LCD supply voltage generator

The LCD supply voltage may be generated on-chip. The

voltage generator is controlled by two internal 6-bit

registers: VA and VB. The nominal LCD operating voltage

at room temperature is given by the relationship:

VOP(nom) = (integer value of register × 0.08) + 1.82

7.2 Programming ranges

Programmed value: 1 to 63. Voltage: 1.90 to 6.86 V.

Tref = 27 °C.

Values producing more than 6.5 V at operating

temperature are not allowed. Operation above this

voltage may damage the device. When programming the

operating voltage the VLCD temperature coefficient must

be taken into account.

Values below 2.2 V are below the specified operating

range of the chip and are therefore not allowed.

Value 0 for VA and VB switches the generator off

(i.e. VA = 0 in character mode, VB = 0 in icon mode).

Usually register VA is programmed with the voltage for

character mode and register VB with the voltage for icon

mode.

When VLCD is generated on-chip the VLCD pads should be

decoupled to VSS with a suitable capacitor. The generated

VLCD is independent of VDD and is temperature

compensated.

When the generator and the direct mode are switched off

an external voltage may be supplied at connected pads

VLCD1. VLCD1 may be higher or lower than VDD.

During direct mode (program DM register bit) the internal

voltage generator is turned off and the VLCD output voltage

is directly connected to VDD2. This reduces the current

consumption during icon mode and Mux 1 : 9 (depending

on the VDD2 value and the LCD liquid properties).

The LCD supply voltage generator ensures that, as long as

VDD is in the valid range (2.2 to 4 V), the required peak

voltage VOP = 6.5 V can be generated at any time.

7.3 LCD bias voltage generator

The intermediate bias voltages for the LCD display are

also generated on-chip. This removes the need for an

external resistive bias chain and significantly reduces the

system current consumption. The optimum value of VLCD

depends on the multiplex rate, the LCD threshold voltage

(Vth) and the number of bias levels. Using a 5-level bias

scheme for 1 : 18 maximum rate allows VLCD < 5 V for

most LCD liquids. The intermediate bias levels for the

different multiplex rates are shown in Table 2. These bias

levels are automatically set to the given values when

switching to the corresponding multiplex rate.

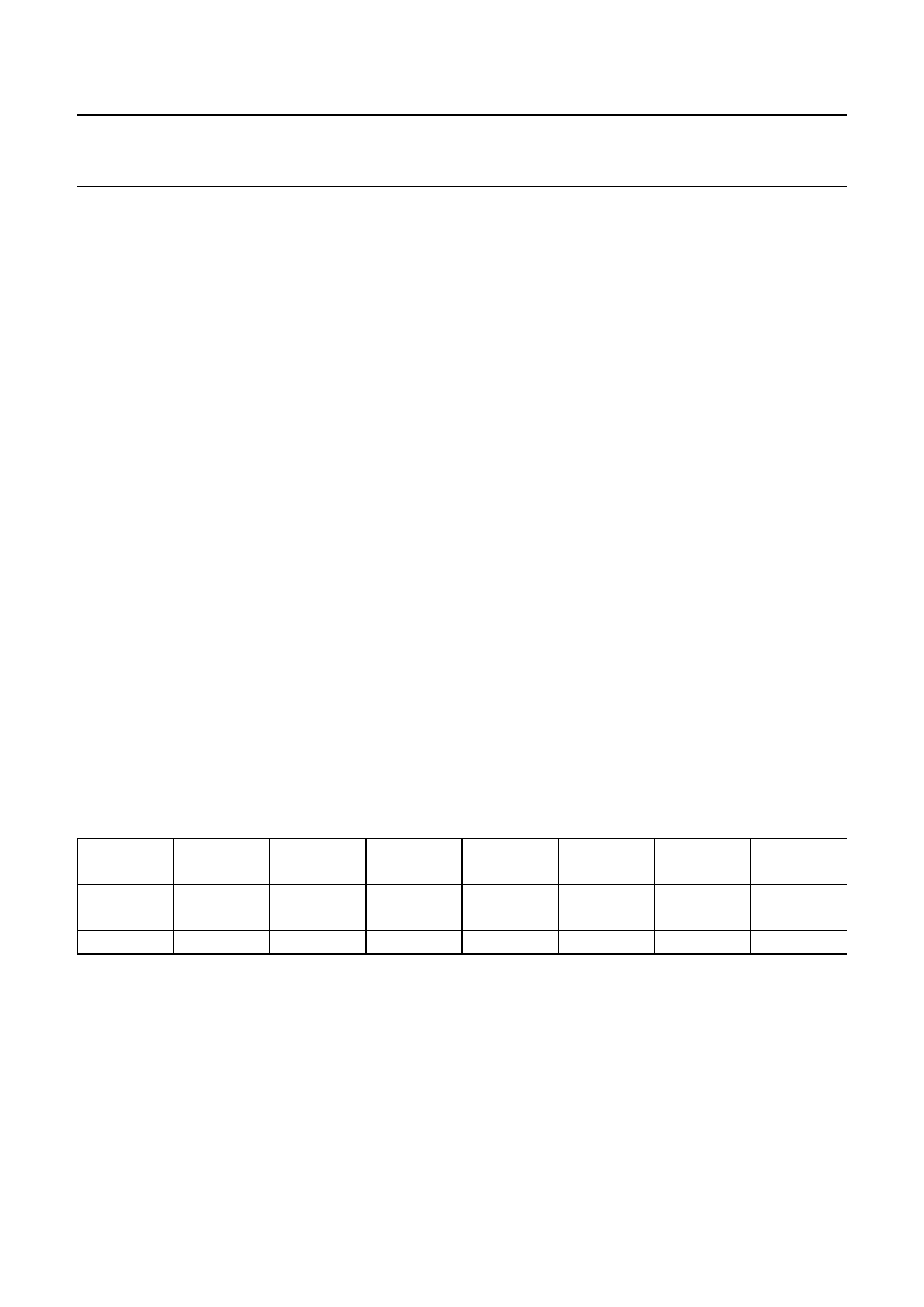

Table 2 Bias levels as a function of multiplex rate

MULTIPLEX NUMBER

RATE OF LEVELS

V1

V2

V3

V4

V5

V6

1 : 18

5

1:9

5

1:2

4

Vop

3/4(1)

1/2

1/2

1/4

Vss

Vop

3/4

1/2

1/2

1/4

Vss

Vop

2/3

2/3

1/3

1/3

Vss

Note

1. The values in the above table are given relative to Vop − Vss, e.g. 3/4 means 3/4 × (Vop − Vss).

2003 Jan 30

7