PCD5003AH Ver la hoja de datos (PDF) - Philips Electronics

Número de pieza

componentes Descripción

Fabricante

PCD5003AH Datasheet PDF : 44 Pages

| |||

Philips Semiconductors

Enhanced Pager Decoder for POCSAG

Product specification

PCD5003A

Alert-only calls only consist of a single address code-word.

Numeric and alphanumeric calls have message

code-words following the address. A message causes the

frame structure to be temporarily suspended. Message

code-words are sent until the message is completed, with

only the sync words being transmitted in their expected

positions.

Message code-words are identified by an MSB of logic 1

and are coded as shown in Fig.3. The message

information is stored in a 20-bit field (bits 2 to 21). The data

format is determined by the call type: 4 bits per digit for

numeric messages and 7 bits per (ASCII) character for

alphanumeric messages.

Each code-word is protected against transmission errors

by 10 CRC check bits (bits 22 to 31) and an even-parity bit

(bit 32). This permits correction of maximum 2 random

errors or up to 3 errors in a burst of 4 bits (a 4-bit burst

error) per code-word.

The POCSAG standard recommends the use of

combinations of data formats and function bits, as given in

Table 1. Other (non-standard) combinations will be

received normally by the PCD5003A. Message data is not

deformatted.

In the PCD5003A error correction methods have been

implemented as shown in Table 2.

Random error correction is default for both address and

message code-words. In addition, burst error correction

can be enabled by SPF programming. Up to 3 erroneous

bits in a 4-bit burst can be corrected.

The error type detected for each code-word is identified in

the message data output to the microcontroller, allowing

rejection of calls with too many errors.

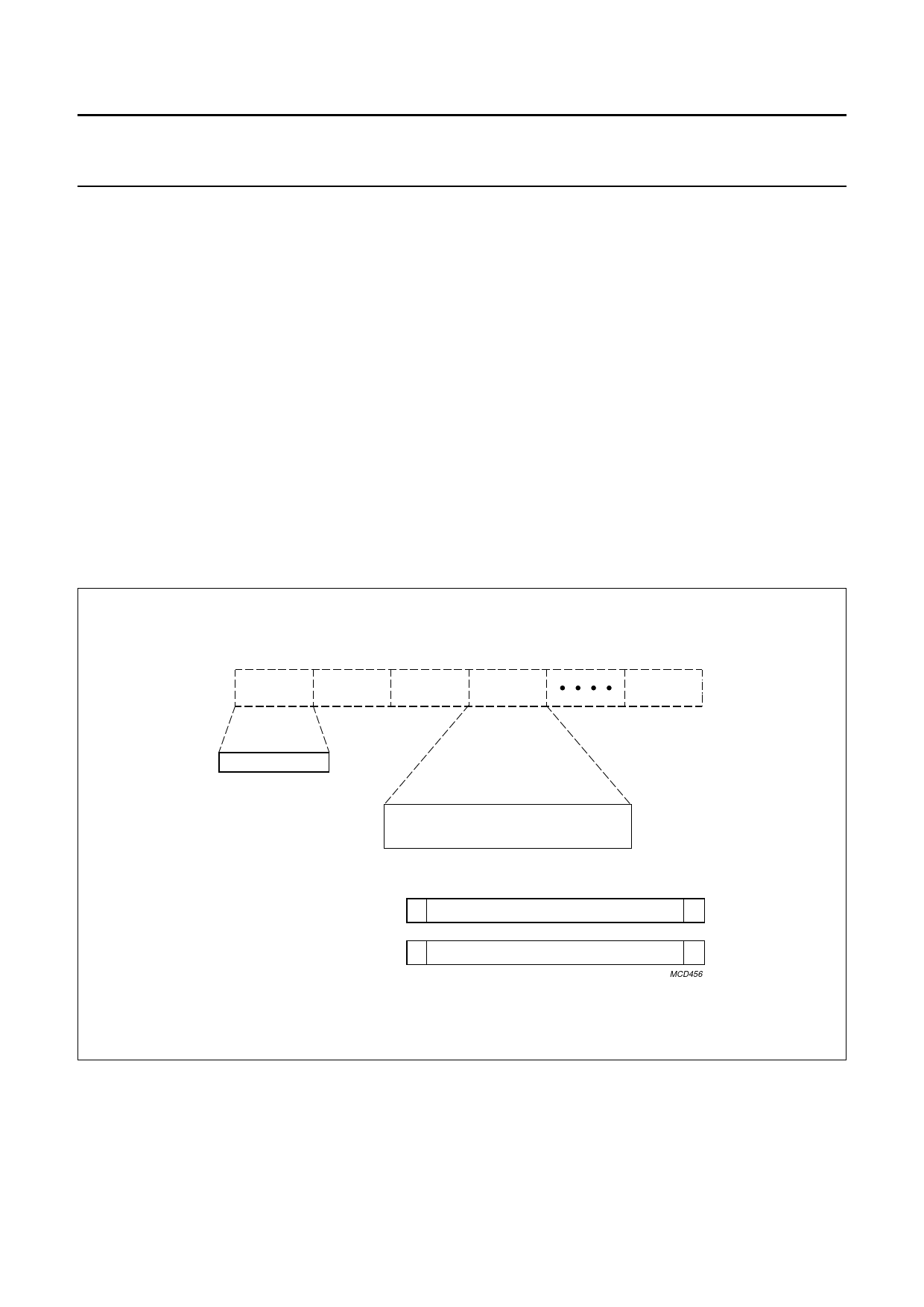

handbook, full pagewidth

PREAMBLE BATCH 1

BATCH 2

BATCH 3

LAST BATCH

10101 . . . 10101010

SYNC | CW CW | CW CW | . . . . . | CW CW

FRAME 0 FRAME 1

FRAME 7

Address code-word 0 18-bit address 2 function bits 10 CRC bits P

Message code-word 1 20-bit message

10 CRC bits P

MCD456

Fig.3 POCSAG code structure.

1999 Jan 08

7