EM78P156E Ver la hoja de datos (PDF) - ELAN Microelectronics

Número de pieza

componentes Descripción

Fabricante

EM78P156E Datasheet PDF : 28 Pages

| |||

EM78P156E

Bit 6 (/PH6)

Control bit used to enable the pull-high of P66 pin.

Bit 7 (/PH7)

Control bit used to enable the pull-high of P67 pin.

• IOCD register is readable and writable.

8. IOCE (WDT Control Register)

7

6

WDTE

EIS

5

4

3

-

ROC

-

2

1

0

-

-

-

Bit 7 (WDTE)

Control bit used to enable Watchdog Timer.

0: Disable WDT.

1: Enable WDT.

• WDTE is both readable and writable.

Bit 6 (EIS)

Control bit used to define the function of P60 (/INT) pin.

0: P60, bi-directional I/O pin.

1: /INT, external interrupt pin. In this case, the I/O control bit of P60 (bit 0 of IOC6) must be set to “1”.

• When EIS is “0”, the path of /INT is masked. When EIS is “1”, the status of /INT pin can also be read by

way of reading Port 6 (R6). Refer to Fig.7(a).

• EIS is both readable and writable.

Bit 4 (ROC)

ROC is used for the R-option.

Setting the ROC to “1” will enable the status of R-option pins (P50~P51) to be read by the controller. Clearing

the ROC will disable the R-option function. If the R-option function is selected, the user must connect the P51

pin or/and P50 pin to VSS by a 430KΩ external resistor (Rex). If the Rex is connected/disconnected, the status

of P50 (P51) will be read as “0”/”1". Refer to Fig.8.

• ROC is readable and writable.

Bits 0~3, 5

Not used.

9. IOCF (Interrupt Mask Register)

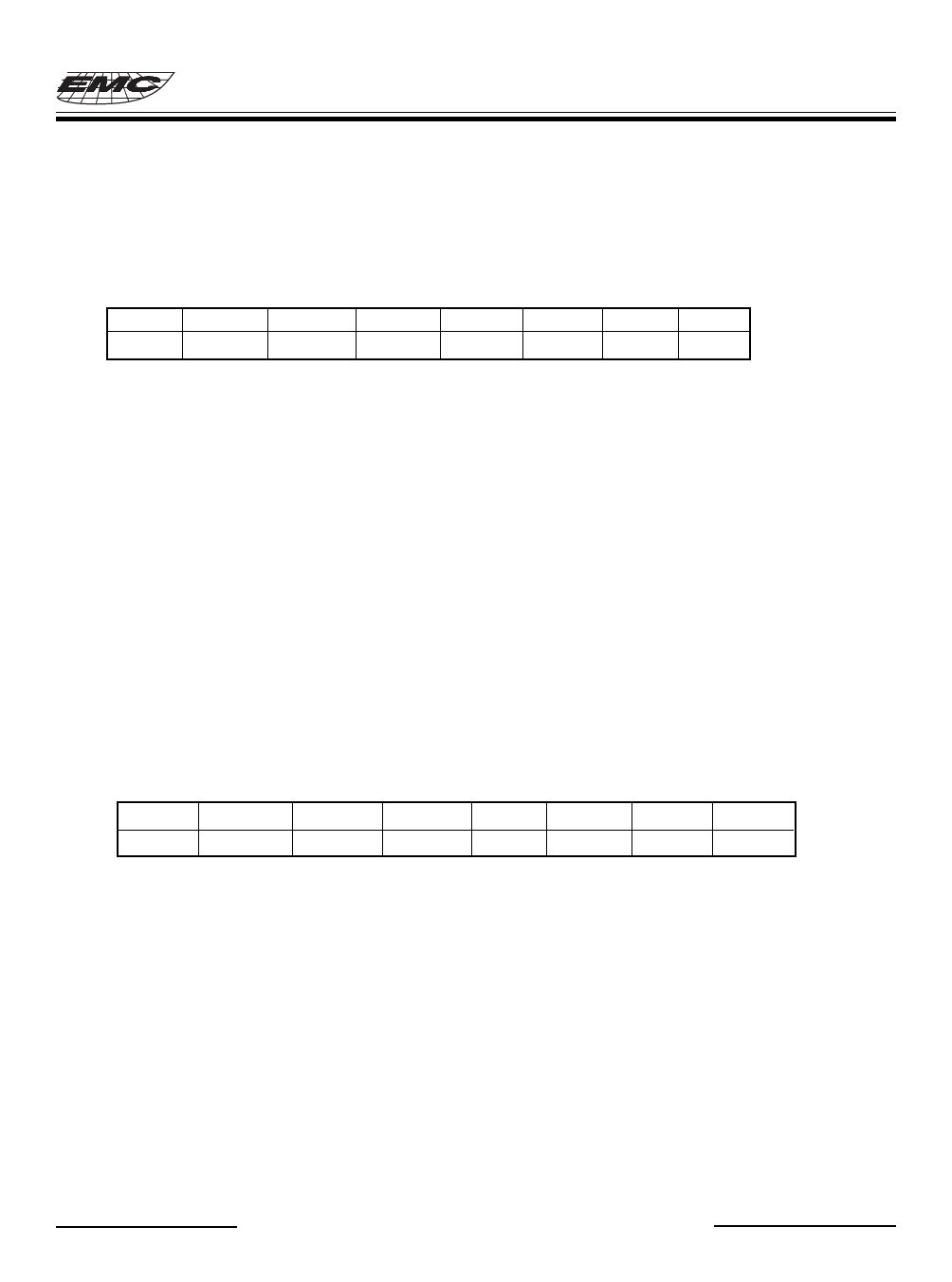

7

6

5

4

3

2

1

0

-

-

-

-

-

EXIE

ICIE

TCIE

Bit 0 (TCIE)

TCIF interrupt enable bit.

0: disable TCIF interrupt

1: enable TCIF interrupt

Bit 1 (ICIE)

ICIF interrupt enable bit.

0: disable ICIF interrupt

1: enable ICIF interrupt

Bit 2 (EXIE)

EXIF interrupt enable bit.

0: disable EXIF interrupt

1: enable EXIF interrupt

Bits 3~7

Not used.

• Individual interrupt is enabled by setting its associated control bit in the IOCF to “1”.

• Global interrupt is enabled by the ENI instruction and is disabled by the DISI instruction. Refer to Fig.10.

• IOCF register is both readable and writable.

* This specification is subject to be changed without notice. 8.11.1999

B3-8