MT8870 Ver la hoja de datos (PDF) - Mitel Networks

Número de pieza

componentes Descripción

Fabricante

MT8870 Datasheet PDF : 12 Pages

| |||

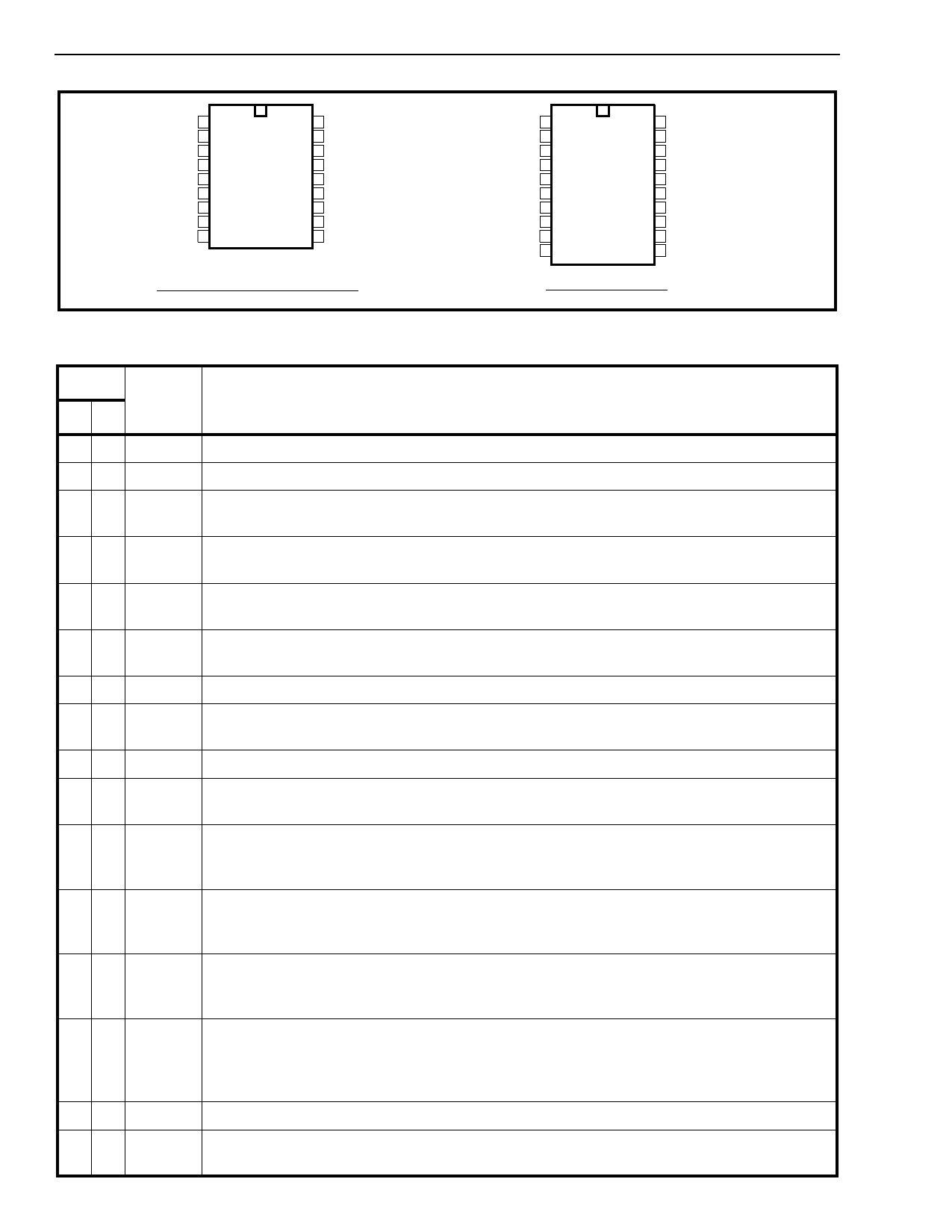

MT8870D/MT8870D-1 ISO2-CMOS

IN+ 1

IN- 2

GS 3

VRef 4

INH 5

PWDN 6

OSC1 7

OSC2 8

VSS 9

18 VDD

17 St/GT

16 ESt

15 StD

14 Q4

13 Q3

12 Q2

11 Q1

10 TOE

18 PIN CERDIP/PLASTIC DIP/SOIC

IN+ 1

IN- 2

GS 3

VRef 4

INH 5

PWDN 6

NC 7

OSC1 8

OSC2 9

VSS 10

20 VDD

19 St/GT

18 ESt

17 StD

16 NC

15 Q4

14 Q3

13 Q2

12 Q1

11 TOE

20 PIN SSOP/TSSOP

Pin Description

Figure 2 - Pin Connections

Pin #

18 20

Name

Description

11

22

33

44

55

66

78

89

9 10

10 11

11- 12-

14 15

15 17

16 18

17 19

18 20

7,

16

IN+

IN-

GS

VRef

INH

PWDN

OSC1

OSC2

VSS

TOE

Q1-Q4

StD

ESt

St/GT

VDD

NC

Non-Inverting Op-Amp (Input).

Inverting Op-Amp (Input).

Gain Select. Gives access to output of front end differential amplifier for connection of

feedback resistor.

Reference Voltage (Output). Nominally VDD/2 is used to bias inputs at mid-rail (see Fig. 6

and Fig. 10).

Inhibit (Input). Logic high inhibits the detection of tones representing characters A, B, C

and D. This pin input is internally pulled down.

Power Down (Input). Active high. Powers down the device and inhibits the oscillator. This

pin input is internally pulled down.

Clock (Input).

Clock (Output). A 3.579545 MHz crystal connected between pins OSC1 and OSC2

completes the internal oscillator circuit.

Ground (Input). 0V typical.

Three State Output Enable (Input). Logic high enables the outputs Q1-Q4. This pin is

pulled up internally.

Three State Data (Output). When enabled by TOE, provide the code corresponding to the

last valid tone-pair received (see Table 1). When TOE is logic low, the data outputs are high

impedance.

Delayed Steering (Output).Presents a logic high when a received tone-pair has been

registered and the output latch updated; returns to logic low when the voltage on St/GT falls

below VTSt.

Early Steering (Output). Presents a logic high once the digital algorithm has detected a

valid tone pair (signal condition). Any momentary loss of signal condition will cause ESt to

return to a logic low.

Steering Input/Guard time (Output) Bidirectional. A voltage greater than VTSt detected at

St causes the device to register the detected tone pair and update the output latch. A

voltage less than VTSt frees the device to accept a new tone pair. The GT output acts to

reset the external steering time-constant; its state is a function of ESt and the voltage on St.

Positive power supply (Input). +5V typical.

No Connection.

4-12