DS1010-80 Ver la hoja de datos (PDF) - Dallas Semiconductor -> Maxim Integrated

Número de pieza

componentes Descripción

Fabricante

DS1010-80 Datasheet PDF : 6 Pages

| |||

NOTES:

1. All voltages are referenced to ground.

DS1010

2. Measured with outputs open.

3. VCC = 5V @ 25°C. Input-to-tap delays accurate on both rising and falling edges within ±2 ns or ±5%

whichever is greater.

4. See “Test Conditions” section.

5. For DS1010 delay lines with a TAP 10 delay of 100 ns or greater, temperature variations from 25°C

to 0°C or 70°C may produce an additional input-to-tap delay shift of ±2ns or ±3%, whichever is

greater.

6. For DS1010 delay lines with a TAP 10 delay less than 100 ns, temperature variations from 25°C to

0°C or 70°C may produce an additional input-to-tap delay shift of ±1 ns or ±9%, whichever is greater.

7. All tap delays tend to vary unidirectionally with temperature or voltage changes. For example, if TAP

1 slows down, all other taps will also slow down; TAP 3 can never be faster than TAP 2.

8. Pulse width and period specifications may be exceeded; however, accuracy will be application-

sensitive (decoupling, layout, etc.).

9. Certain high-frequency applications not recommended for -50 in 16-pin package. Consult factory.

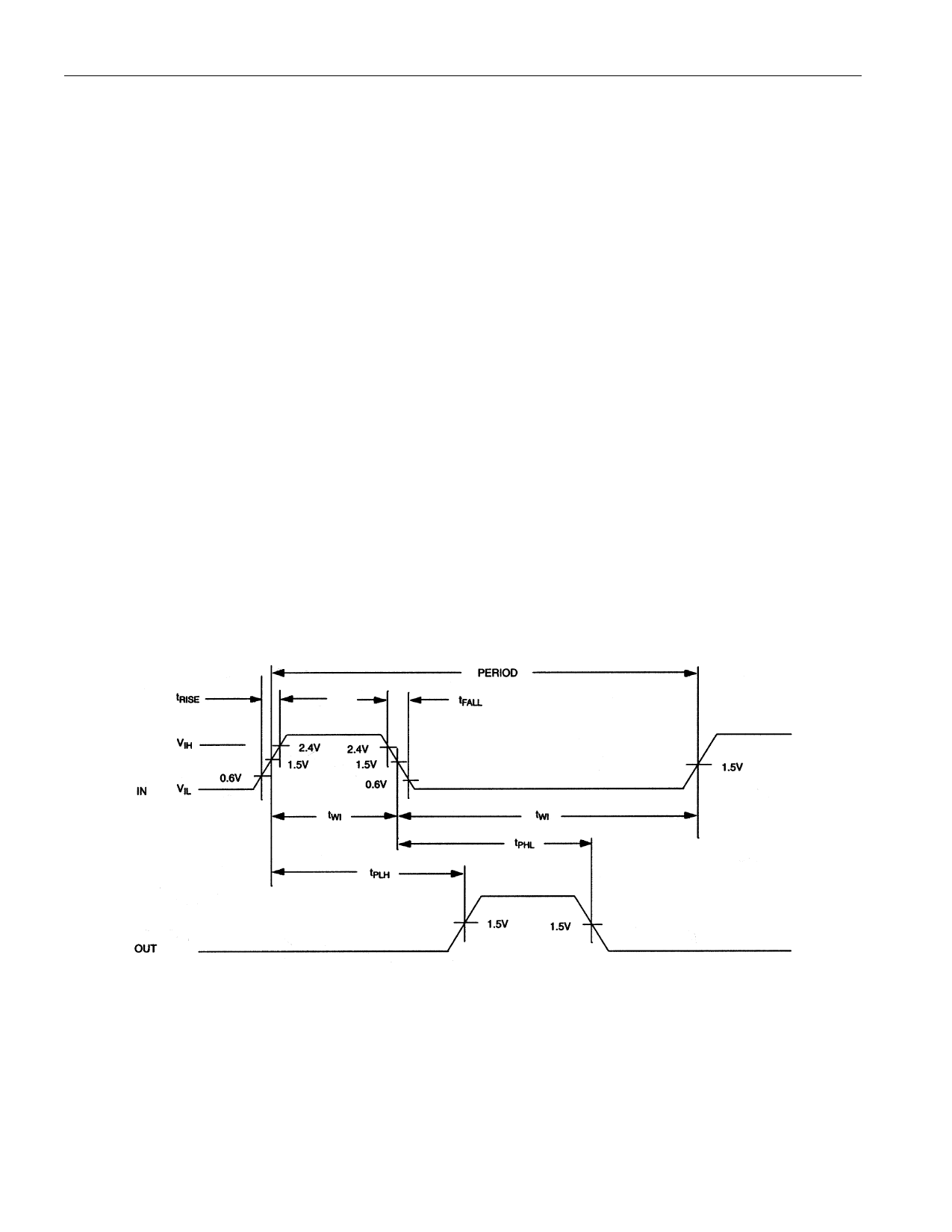

TIMING DIAGRAM: SILICON DELAY LINE Figure 2

4 of 6