MSC7110 Ver la hoja de datos (PDF) - Freescale Semiconductor

Número de pieza

componentes Descripción

Fabricante

MSC7110 Datasheet PDF : 8 Pages

| |||

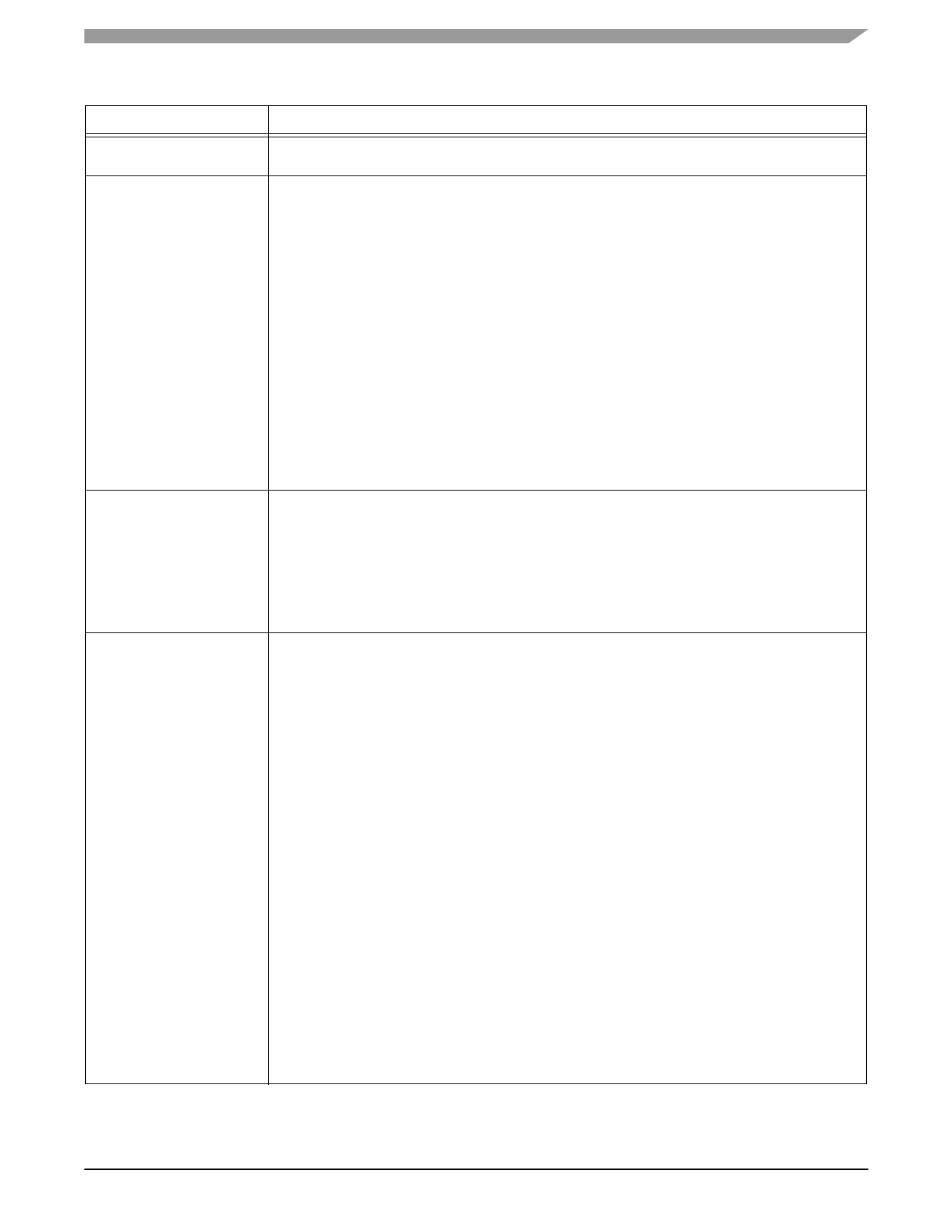

Features

Feature

Host Interface (HDI16)

TDM Module

Timers

UART

Table 1. MSC7110 Features (Continued)

Description

Enhanced 16-bit wide interface provides a glueless connection to industry-standard

microcontrollers, microprocessors, and DSPs.

TDM module with the following features:

• Totally independent receive and transmit, each having one data line, one clock line, and one

frame sync line.

• Frame sync line and/or clock line can be shared between receive and transmit.

• Glueless interface to E1/T1 frames and MVIP, SCAS, and H.110 buses.

• Hardware A-law/µ-law conversion

• Up to 50 Mbps (50 MHz bit clock).

• Maximum rate is 1/4 the core frequency.

• Up to 128 channels.

• Each channel can be programmed to be active or inactive.

• 8- or 16-bit word widths.

• The TDM Sync Signal (TDMxTFS/TDMxRFS) can be configured as either input or output.

• The TDM clock signal (TDMxTCK/TDMxRCK) can be configured as either input or output.

• Frame sync and data signals can be programmed to be sampled either on the rising edge or

on the falling edge of the clock.

• Frame sync can be programmed as active low or active high.

• Selectable delay (0–3 bits) between the Frame Sync signal and the beginning of the frame.

• MSB or LSB first support.

Two 16-bit quad timers, each with the following features:

• Cyclic or one-shot.

• Input clock polarity control.

• Interrupt request when counting reaches a programmed threshold.

• Pulse or level interrupts.

• Dynamically updated programmed threshold.

• Read counter any time.

• Maximum rate is 1/4 the core frequency.

• Two signals for transmit data and receive data.

• No clock, asynchronous mode.

• Full-duplex operation.

• Standard mark/space non-return-to-zero (NRZ) format.

• 13-bit baud rate selection.

• Programmable 8-bit or 9-bit data format.

• Separately enabled transmitter and receiver.

• Programmable transmitter output polarity.

• Two receiver wake-up methods:

• Idle line wake-up.

• Address mark wake-up.

• Separate receiver and transmitter interrupt requests.

• Eight flags, the first five can generate interrupt request:

• Transmitter empty.

• Transmission complete.

• Receiver full.

• Idle receiver input.

• Receiver overrun.

• Noise error.

• Framing error.

• Parity error.

• Receiver framing error detection.

• Hardware parity checking.

• 1/16 bit-time noise detection.

• Maximum bit rate 5.0 Mbps.

• Single-wire and loop operations.

MSC7110 Product Brief, Rev. 2

Freescale Semiconductor

3