MEJ02C2016_M5M5J167KT Ver la hoja de datos (PDF) - Hitachi -> Renesas Electronics

Número de pieza

componentes Descripción

Fabricante

MEJ02C2016_M5M5J167KT

MEJ02C2016_M5M5J167KT Datasheet PDF : 11 Pages

| |||

Jan.10,2003 Ver. 2.1

M5M5J167KT - 70HI

MITSUBISHI LSIs

16777216-BIT (1048576-WORD BY 16-BIT / 2097152-WORD BY 8-BIT) CMOS STATIC RAM

FUNCTION

The M5M5J167KT is organized as 1048576-words by 16-

bit / 2097152-words by 8-bit. These dev ices operate on a

single +2.7~3.6V power supply , and are directly TTL

compatible to both input and output. Its f ully static circuit

needs no clocks and no ref resh, and makes it usef ul.

The operation mode are determined by a combination of

the dev ice control inputs BC1# , BC2# , S1#, S2 , W#,

OE# and BY TE#. Each mode is summarized in the f unction

table. The address select A19 can select either one

8MSRAM chip or another 8MSRAM chip.

A write operation is executed whenev er the low lev el W#

ov erlaps with the low lev el BC1# and/or BC2# and the low

lev el S1# and the high lev el S2. The address (A-1~A19 :

By te mode, A0~A19 : Word mode) must be set up bef ore

the write cy c le and must be stable during the entire cy cle.

A read operation is executed by s etting W# at a high

lev el and OE# at a low lev el while BC1# and/or BC2# and

S1#and S2 are in an activ e state (S1#=L, S2=H).

When setting BYTE# at a low lev el, the f unction will be

in the x8 mede, which is, DQ1-8 are av ailable and DQ9-16

are not av ailable. In the x8 mode, A-1 is used as the

additional address. During the activ e f unction f or x8 mode,

BC1# BC2# must be low lev el.

When setting BC1# and BC2# at a high lev el or S1# at

a high lev el or S2 at a low lev el, the chips are in a non-

selectable mode in which both reading and writing are

disabled.

In this mode, the output stage is in a high-impedance state,

allowing OR-tie with other chips and memory expansion by

BC1#, BC2# and S1#, S2.

The power supply c urrent is reduced as low as 0.2µA

(25°C, ty pical), and the memory data can be held at +2.0V

power supply , enabling battery back-up operation during

power f ailure or power-down operation in the non-selected

mode.

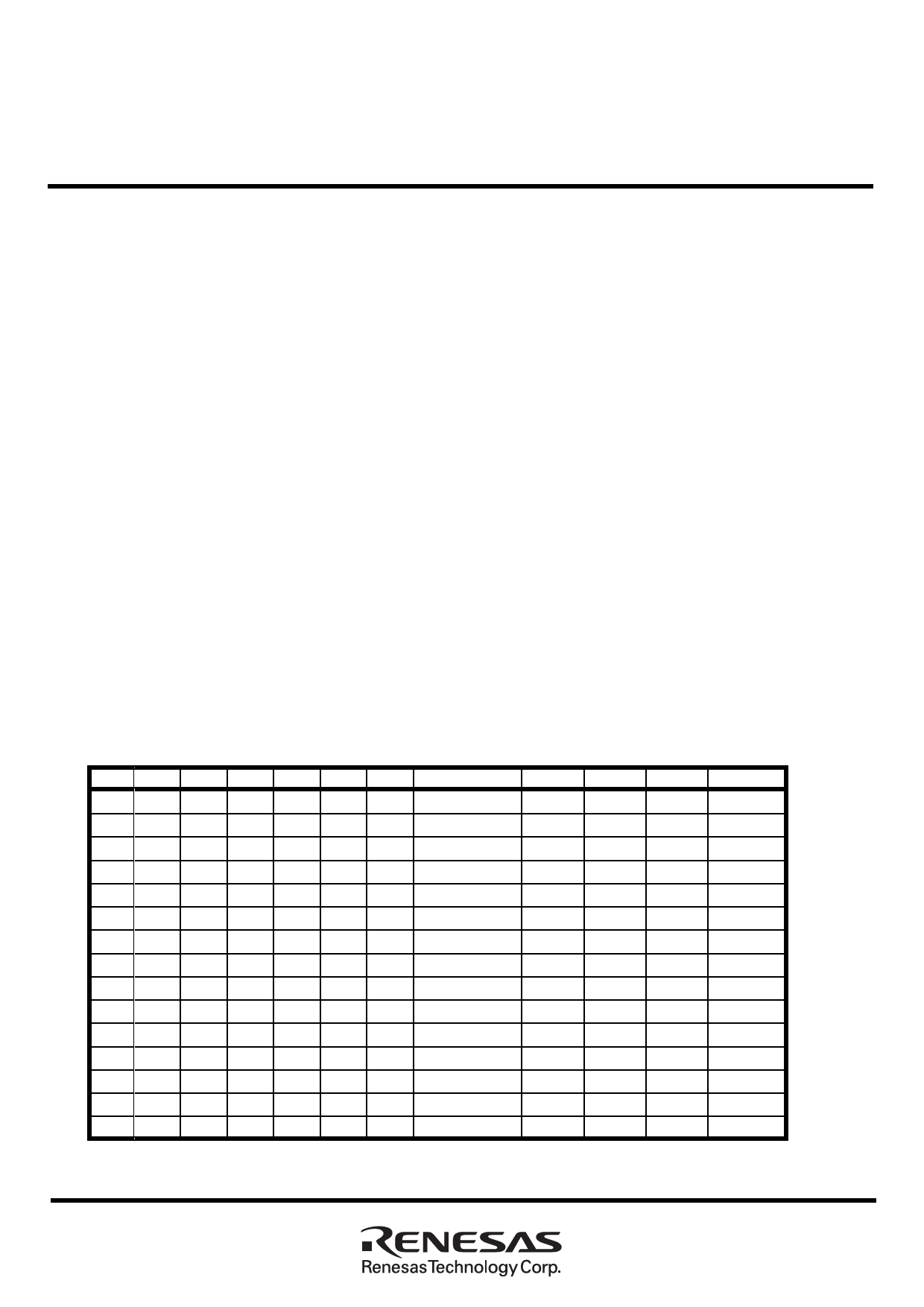

FUNCTION TABLE

S1# S2 BYTE# BC1# BC2# W# OE#

Mode

H

H

X

X

X

X

X Non selection

X

L

X

X

X

X

X Non selection

X

X

H

H

H

X

X Non selection

L

H

H

L

H

L

X

Write

L

H

H

L

H

H

L

Read

L

H

H

L

H

H

H

-------

L

H

HH

L

L

X

Write

L

H

H

H

L

H

L

Read

L

H

H

H

L

H

H

-------

L

H

H

L

L

L

X

Write

L

H

H

L

L

H

L

Read

L

H

H

L

L

H

H

-------

L

H

L

L

L

L

X

Write

L

H

L

L

L

H

L

Read

L

H

L

L

L

H

H

-------

Note1 : "H" and "L" in this table mean VIH and VIL, respectiv ely .

Note2 : "X" in this table should be "H" or "L".

DQ1~8 DQ9~15 DQ16

High-Z High-Z High-Z

High-Z High-Z High-Z

High-Z High-Z High-Z

Din High-Z High-Z

Dout High-Z High-Z

High-Z High-Z High-Z

High-Z Din

Din

High-Z Dout Dout

High-Z High-Z High-Z

Din

Din

Din

Dout Dout Dout

High-Z High-Z High-Z

Din High-Z A-1

Dout High-Z A-1

High-Z High-Z A-1

Icc

Standby

Standby

Standby

Active

Active

Active

Active

Active

Active

Active

Active

Active

Active

Active

Active

2