LTC1740IGPBF Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Fabricante

LTC1740IGPBF Datasheet PDF : 16 Pages

| |||

LTC1740

APPLICATIO S I FOR ATIO

Conversion Details

The LTC1740 is a high performance 14-bit A/D converter

that operates up to 6Msps. It is a complete solution with

an on-chip sample-and-hold, a 14-bit pipelined CMOS

ADC and a low drift programmable reference. The digital

output is parallel, with a 14-bit two’s complement format

and an out-of-range (overflow) bit.

The rising edge of the CLK begins the conversion. The

differential analog inputs are simultaneously sampled and

passed on to the pipelined A/D. After two more conversion

starts (plus a 100ns conversion time) the digital outputs

are updated with the conversion result and will be ready for

capture on the third rising clock edge. Thus even though

a new conversion is begun every time CLK goes high, each

result takes three clock cycles to reach the output.

The analog signals that are passed from stage to stage in

the pipelined A/D are stored on capacitors. The signals on

these capacitors will be lost if the delay between conver-

sions is too long. For accurate conversion results, the part

should be clocked faster than 50kHz.

In some pipelined A/D converters if there is no clock present,

dynamic logic on the chip will droop and the power con-

sumption sharply increases. The LTC1740 doesn’t have

this problem. If the part is not clocked for 1ms, an internal

timer will refresh the dynamic logic. Thus the clock can be

turned off for long periods of time to save power.

Power Supplies

The LTC1740 will operate from either a single 5V or dual

±5V supply, making it easy to interface the analog input to

single or dual supply systems. The digital output drivers

have their own power supply pin (OVDD) which can be set

from 3V to 5V, allowing direct connection to either 3V or

+ +AIN

VIN

–AIN

–

VREF

±VREF

1.8

ADC

CORE

1740 F01

Figure 1. Analog Input Circuit

5V digital systems. For single supply operation, VSS should

be connected to analog ground. For dual supply operation,

VSS should be connected to – 5V. All VDD pins should be

connected to a clean 5V analog supply. (Don’t connect VDD

to a noisy system digital supply.)

Analog Input Range

The LTC1740 has a flexible analog input with a wide

selection of input ranges. The input range is always

differential and is set by the voltage at the VREF pin

(Figure␣ 1). The input range of the A/D core is fixed at

±VREF/1.8. The reference voltage, VREF, is either set by the

on-chip voltage reference or directly driven by an external

voltage.

Internal Reference

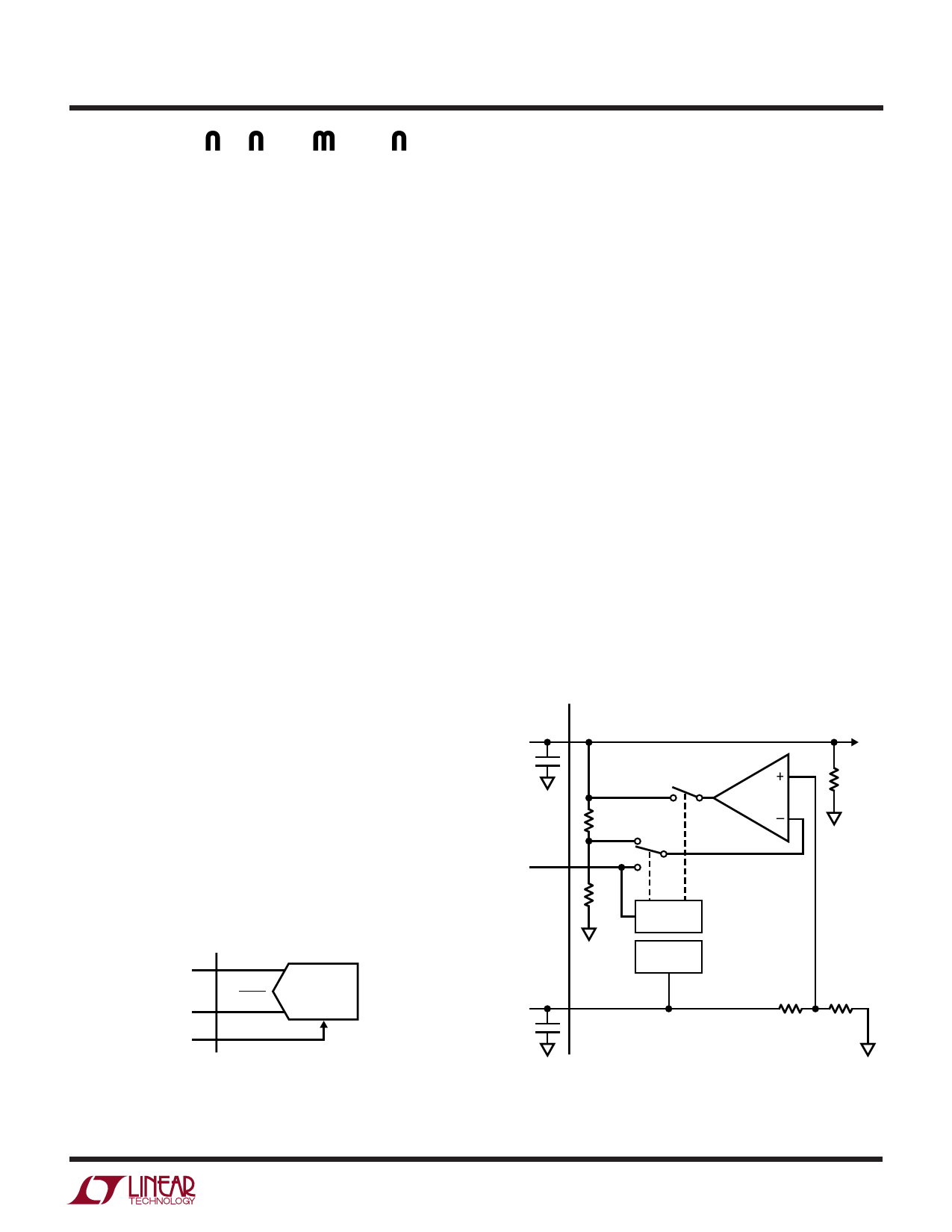

Figure 2 shows a simplified schematic of the LTC1740

reference circuitry. An on-chip temperature compensated

bandgap reference (VCM) is factory trimmed to 2.500V.

The voltage at the VREF pin sets the input span of the ADC

to ±VREF/1.8. An internal voltage divider converts VCM to

2.250V, which is connected to a reference amplifier. The

reference programming pin, SENSE, controls how the

VREF

1µF

SENSE

VCM

1µF

R1

5k

R2

5k

LOGIC

2.5V

REFERENCE

TO

ADC

1k

2.250V

1740 F02

Figure 2. Reference Circuit

1740f

9