LT3580EDD-TRPBF Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Fabricante

LT3580EDD-TRPBF

LT3580EDD-TRPBF Datasheet PDF : 28 Pages

| |||

LT3580

APPLICATIONS INFORMATION

(1) SYNC may not toggle outside the frequency range of

200kHz to 2.5MHz unless it is stopped low to enable

the free-running oscillator.

(2) The SYNC frequency can always be higher than the

free-running oscillator frequency, fOSC , but should not

be less than 25% below fOSC.

Operating Frequency Selection

There are several considerations in selecting the operating

frequency of the converter. The first is staying clear of

sensitive frequency bands, which cannot tolerate any

spectral noise. For example, in products incorporating RF

communications, the 455kHz IF frequency is sensitive to

any noise, therefore switching above 600kHz is desired.

Some communications have sensitivity to 1.1MHz, and in

that case, a 1.5MHz switching converter frequency may be

employed. The second consideration is the physical size

of the converter. As the operating frequency goes up, the

inductor and filter capacitors go down in value and size.

The tradeoff is efficiency, since the switching losses due

to NPN base charge (see Thermal Calculations), Schottky

diode charge, and other capacitive loss terms increase

proportionally with frequency.

Soft-Start

The LT3580 contains a soft-start circuit to limit peak switch

currents during start-up. High start-up current is inherent

in switching regulators in general since the feedback loop

is saturated due to VOUT being far from its final value. The

regulator tries to charge the output capacitor as quickly as

possible, which results in large peak currents.

The start-up current can be limited by connecting an

external capacitor (typically 100nF to 1μF) to the SS pin.

This capacitor is slowly charged to ~2.2V by an internal

275k resistor once the part is activated. SS pin voltages

below ~1.1V reduce the internal current limit. Thus, the

gradual ramping of the SS voltage also gradually increases

the current limit as the capacitor charges. This, in turn,

allows the output capacitor to charge gradually toward its

final value while limiting the start-up current.

In the event of a commanded shutdown or lockout (SHDN

pin), internal undervoltage lockout (UVLO) or a thermal

lockout, the soft-start capacitor is automatically discharged

to ~200mV before charging resumes, thus assuring that

the soft-start occurs after every reactivation of the chip.

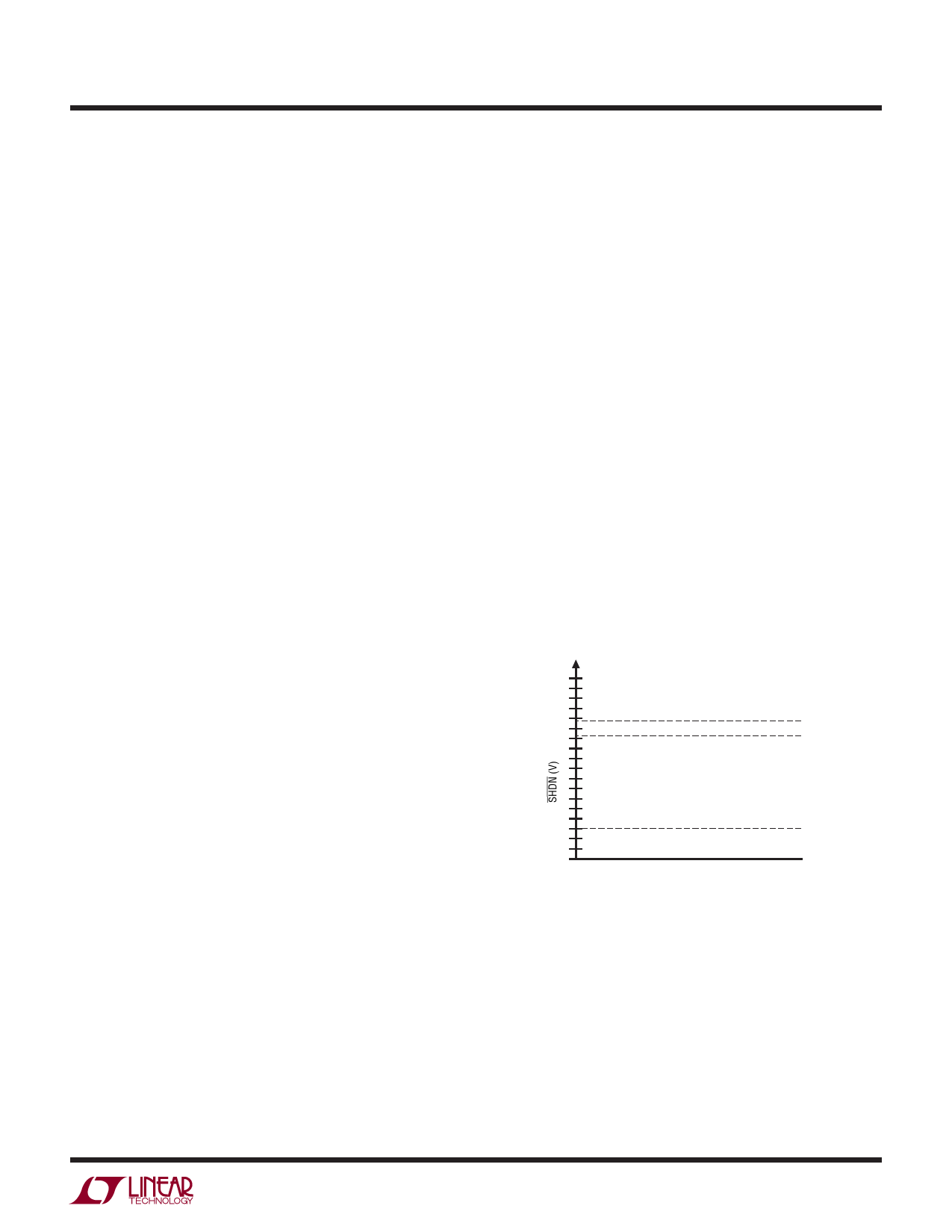

Shutdown

The SHDN pin is used to enable or disable the chip.

For most applications, SHDN can be driven by a digital

logic source. Voltages above 1.38V enable normal active

operation. Voltages below 300mV will shutdown the chip,

resulting in extremely low quiescent current.

While the SHDN voltage transitions through the lockout

voltage range (0.3V to 1.24V) the power switch is disabled

and the SR2 latch is set (see the Block Diagram). This

causes the soft-start capacitor to begin discharging,

which continues until the capacitor is discharged and

active operation is enabled. Although the power switch

is disabled, SHDN voltages in the lockout range do not

necessarily reduce quiescent current until the SHDN voltage

is near or below the shutdown threshold.

Also note that SHDN can be driven above VIN or VOUT as

long as the SHDN voltage is limited to less than 32V.

1.38V

1.24V

ACTIVE

(NORMAL OPERATION)

(HYSTERESIS AND TOLERANCE)

LOCKOUT

(POWER SWITCH OFF,

SS CAPACITOR DISCHARGED)

0.3V

SHUTDOWN

0.0V

(LOW QUIESCENT CURRENT)

3580 F06

Figure 6. Chip States vs SHDN Voltage

Configurable Undervoltage Lockout

Figure 7 shows how to configure an undervoltage lockout

(UVLO) for the LT3580. Typically, UVLO is used in situations

where the input supply is current-limited, has a relatively

high source resistance, or ramps up/down slowly. A

switching regulator draws constant power from the source,

so source current increases as source voltage drops. This

looks like a negative resistance load to the source and can

cause the source to current-limit or latch low under low

3580fg

13