LT3489 Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Fabricante

LT3489 Datasheet PDF : 12 Pages

| |||

LT3489

PI FU CTIO S

VC (Pin 1): Error Amplifier Output Pin. Tie external compen-

sation network to this pin, or use the internal compensation

network by shorting the VC pin to the COMP pin.

FB (Pin 2): Feedback Pin. Reference voltage is 1.235V.

Connect resistive divider tap here. Minimize the trace area at

FB. Set VOUT according to VOUT = 1.235 • (1 + R1/R2).

SHDN (Pin 3): Shutdown Pin. Tie to 2V or more to enable

device. Ground to shut down. Do not float this pin.

GND (Pin 4): Ground. Tie directly to local ground plane.

SW (Pin 5): Switch Pin. This is the collector of the internal

NPN power switch. Minimize the metal trace area connected

to this pin to minimize EMI.

VIN (Pin 6): Input Supply Pin. Must be locally bypassed.

COMP (Pin 7): Internal Compensation Pin. Provides an

internal compensation network. Tie directly to the VC pin

for internal compensation. Tie to GND if not in use.

SS (Pin 8): Soft-Start Pin. Place a soft-start capacitor here.

Upon start-up, 10μA of current charges the capacitor to

1.8V. Use a larger capacitor for slower start-up. Leave

floating if not in use.

Exposed Pad (Pin 9): Ground. Must be soldered to

PCB.

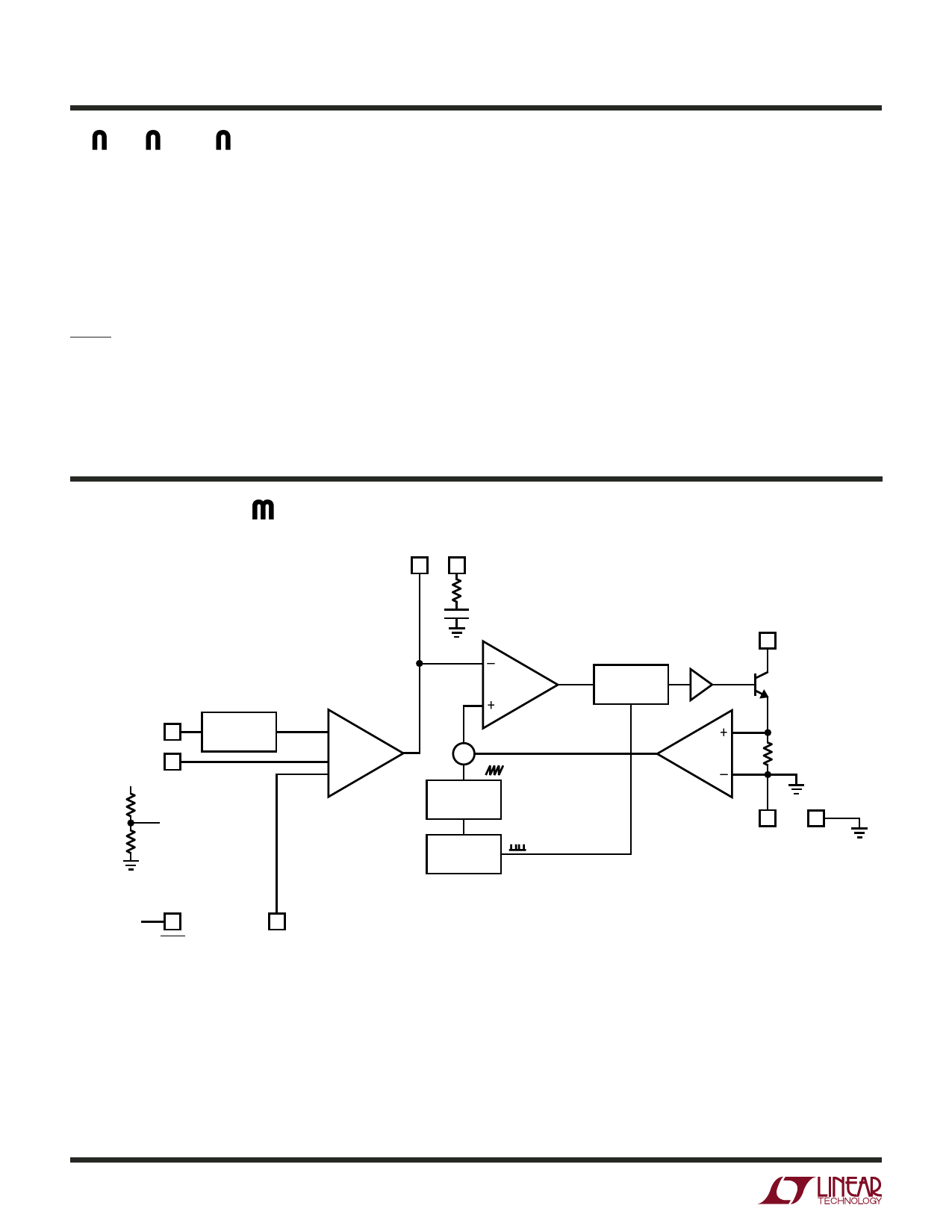

BLOCK DIAGRA

VIN

6

SS 8

VOUT

1.235V

REFERENCE

R1 (EXTERNAL)

FB

R2 (EXTERNAL)

+

+ A1

–

VC COMP

1

7

100k

125pF

–

COMPARATOR

A2

+

R

Q

S

SW

5

DRIVER

Q1

Σ

RAMP

GENERATOR

2MHz

OSCILLATOR

0.01Ω

4

GND

9

GND

3489 F01

SHUTDOWN

3

2

SHDN

FB

Figure 1. Block Diagram

3489f

4