LT1372IN8 Ver la hoja de datos (PDF) - Linear Technology

Número de pieza

componentes Descripción

Fabricante

LT1372IN8 Datasheet PDF : 12 Pages

| |||

UU W U

APPLICATIO S I FOR ATIO

Positive fixed voltage versions are available (consult

Linear Technology marketing).

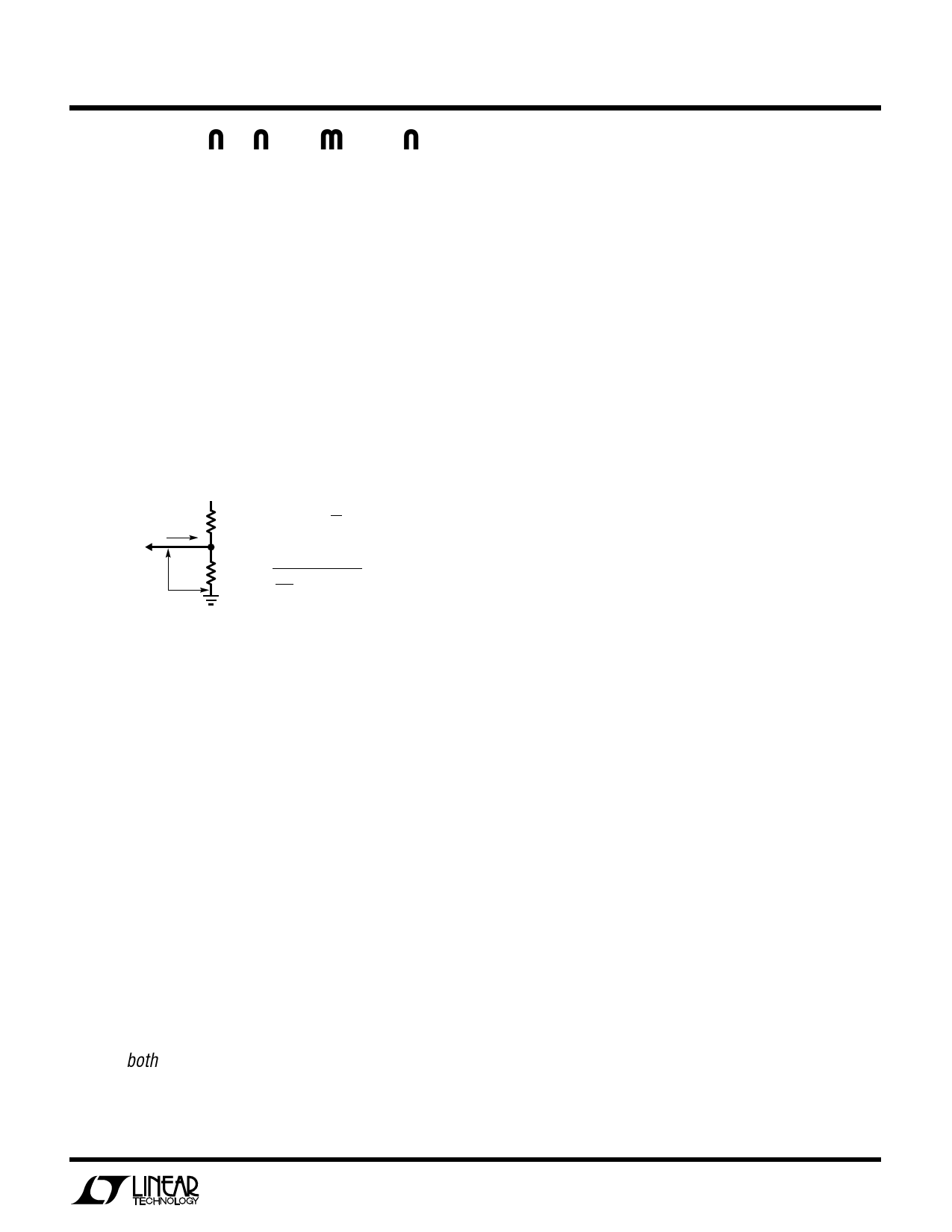

Negative Output Voltage Setting

The LT1372/LT1377 develops a – 2.49V reference (VNFR)

from the NFB pin to ground. Output voltage is set by

connecting the NFB pin to an output resistor divider

(Figure 2). The – 30µA NFB pin bias current (INFB) can

cause output voltage errors and should not be ignored.

This has been accounted for in the formula in Figure 2. The

suggested value for R2 is 2.49k. The FB pin is normally left

open for negative output application. See Dual Polarity

Output Voltage Sensing for limitatins on FB pin loading

when using the NFB pin.

–VOUT

INFB

R1

NFB

PIN

R2

VNFR

( ) –VOUT = VNFB

1

+

R1

R2

+ INFB (R1)

( ) ( ) R1 = VOUT– 2.49

2.49

R2

+

30 × 10–6

LT1372 • F02

Figure 2. Negative Output Resistor Divider

Dual Polarity Output Voltage Sensing

Certain applications benefit from sensing both positive

and negative output voltages. One example is the “Dual

Output Flyback Converter with Overvoltage Protection”

circuit shown in the Typical Applications section. Each

output voltage resistor divider is individually set as de-

scribed above. When both the FB and NFB pins are used,

the LT1372/LT1377 acts to prevent either output from

going beyond its set output voltage. For example in this

application, if the positive output were more heavily loaded

than the negative, the negative output would be greater

and would regulate at the desired set-point voltage. The

positive output would sag slightly below its set-point

voltage. This technique prevents either output from going

unregulated high at no load. Please note that the load on

the FB pin should not exceed 250µA when the NFB pin is

used. This situation occurs when the resistor dividers are

used at both FB and NFB. True load on FB is not the full

divider current unless the positive output is shorted to

ground. See Dual Output Flyback Converter application.

LT1372/LT1377

Shutdown and Synchronization

The dual function S/S pin provides easy shutdown and

synchronization. It is logic level compatible and can be

pulled high, tied to VIN or left floating for normal operation.

A logic low on the S/S pin activates shutdown, reducing

the part’s supply current to 12µA. Typical synchronization

range is from 1.05 to 1.8 times the part’s natural switching

frequency, but is only guaranteed between 600kHz and

800kHz (LT1372) or 1.2MHz and 1.6MHz (LT1377). A

12µs resetable shutdown delay network guarantees the

part will not go into shutdown while receiving a synchro-

nization signal.

Caution should be used when synchronizing above 700kHz

(LT1372) or 1.4MHz (LT1377) because at higher sync

frequencies the amplitude of the internal slope compensa-

tion used to prevent subharmonic switching is reduced.

This type of subharmonic switching only occurs when the

duty cycle of the switch is above 50%. Higher inductor

values will tend to eliminate problems.

Thermal Considerations

Care should be taken to ensure that the worst-case input

voltage and load current conditions do not cause exces-

sive die temperatures. The packages are rated at 120°C/W

for SO (S8) and 130°C/W for PDIP (N8).

Average supply current (including driver current) is:

IIN = 4mA + DC (ISW/60 + ISW × 0.004)

ISW = switch current

DC = switch duty cycle

Switch power dissipation is given by:

PSW = (ISW)2 × RSW × DC

RSW = output switch “On” resistance

Total power dissipation of the die is the sum of supply

current times supply voltage plus switch power:

PD(TOTAL) = (IIN × VIN) + PSW

7