LB1923M Ver la hoja de datos (PDF) - SANYO -> Panasonic

Número de pieza

componentes Descripción

Fabricante

LB1923M Datasheet PDF : 17 Pages

| |||

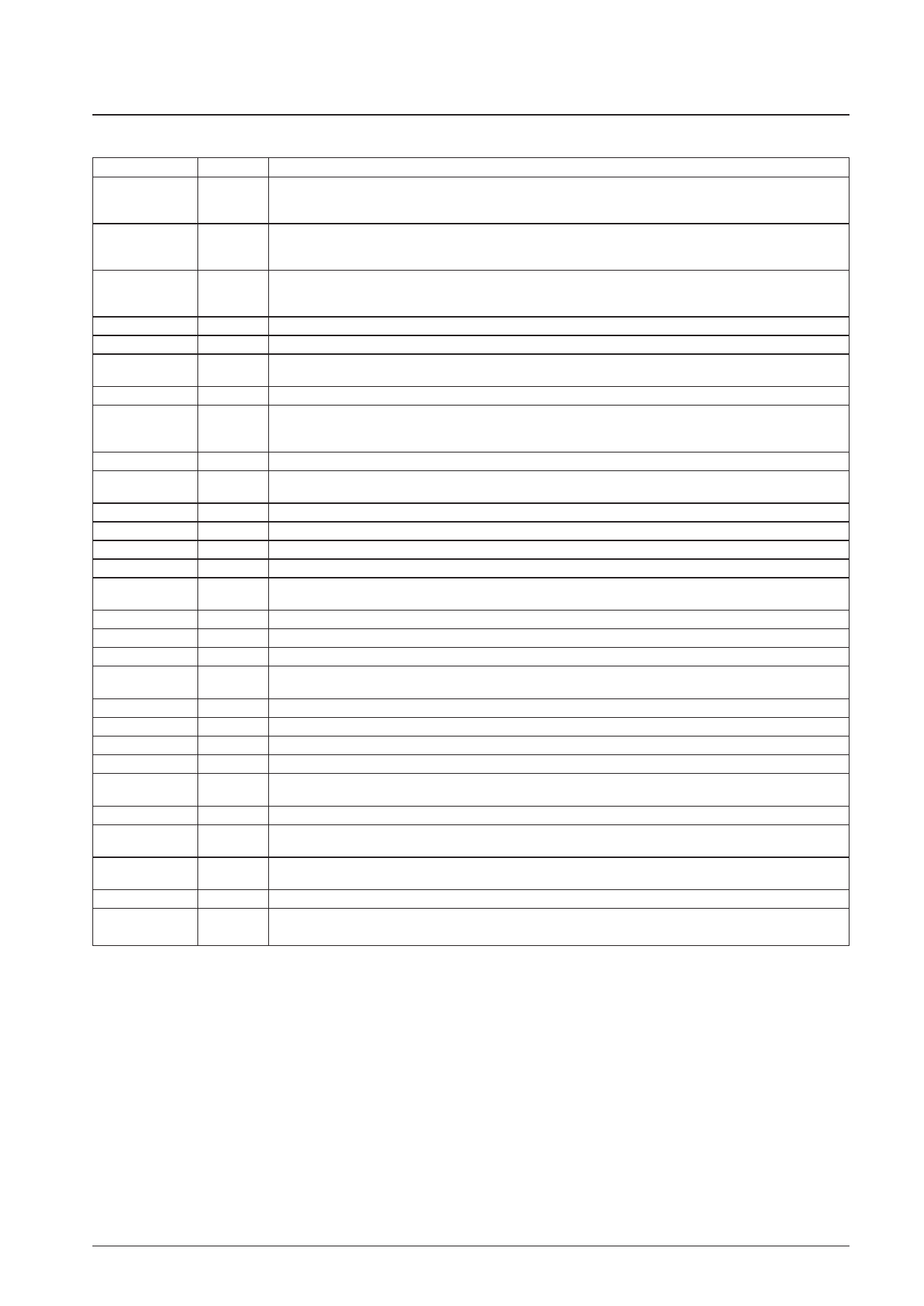

LB1923M

Pin Functions

Pin

IN1+, IN1–

IN2+, IN2–

IN3+, IN3–

UH

VH

WH

UL

VL

WL

VCC

VREG

GND

CR

CROCK

R

C

FILI

FILO

DOUT

ROUT

LD

INTREF

INTIN

INTOUT

TOC

FGIN+

FGIN–

FGOUT

FGSOUT

RF

S/S

F/R

BR

CLK

N1

N2

Pin No.

19, 20

21, 22

23, 24

27

29

31

26

28

30

32

33

16 to 18

38 to 40

34

35

36

37

42

41

3

4

5

43

2

1

44

15

14

13

12

25

9

7

6

8

10

11

Function

Hall inputs for the phases

The logic high level corresponds to the state VIN+ > VIN–.

Outputs. These are fixed-current source outputs.

The duty is controlled by the output pin PWM.

These are open collector sink outputs.

A capacitor must be inserted between this pin and ground to prevent noise entering the circuit.

7-V shunt regulator output

Ground

Used to set the PWM circuit oscillator frequency.

Motor lock protection circuit. Reference signal oscillator connection. Used by the circuit that prevents incorrect

operation if the clock line is disconnected.

A capacitor must be inserted between this pin and ground.

VCO circuit. This pin sets the charge and discharge current. A resistor must be inserted between this pin and ground.

VCO oscillator connection. A capacitor must be inserted between this pin and ground. Select a value for that capacitor

such that the C pin oscillator frequency does not exceed 1 MHz.

Inverting input to the VCO filter amplifier. This pin is connected to the VCO PLL through an (IC internal) 10-kW resistor.

VCO filter amplifier output. This pin is connected to the VCO circuit internally.

Speed discriminator output. A low level is output when the motor is over speed.

PLL circuit output. Outputs the result of the phase comparison between 1/2fCLK and 1/2fFG.

Lock detection output. This is an open collector output.

This pin outputs a low level when the motor speed is within the locked range (±6.25%).

Integrating amplifier noninverting input (the 1/2 VCC potential)

Integrating amplifier inverting input

Integrating amplifier output

Torque command input. Normally, this pin is connected to the INTOUT pin. Lowering the TOC pin potential increases

the torque by changing the PWM signal duty for the UL, VL, and WL outputs.

FG amplifier noninverting input (the 1/2 VCC potential). A capacitor must be inserted between this pin and ground.

FG amplifier inverting input

FG amplifier output

FG amplifier (post-Schmitt) output. This is an open collector output.

Output current detection. A resistor must be inserted between this pin and ground.

This resistor sets the maximum output current IOUT to be 0.5/Rf.

Start/stop control input. Apply a low level for start, and either a high level or an open (high-impedance) state for start.

Forward/reverse control input. Apply a low level for forward, and either a high level or an open (high-impedance) state

for reverse.

Braking control input (short braking operation). Apply a low level for start, and either a high level or an open (high-

impedance) state to brake the motor.

External clock signal input. 10 kHz max.

Speed discriminator count value selection inputs

No. 6067-6/17