L6563 Ver la hoja de datos (PDF) - STMicroelectronics

Número de pieza

componentes Descripción

Fabricante

L6563 Datasheet PDF : 37 Pages

| |||

L6563 - L6563A

Description

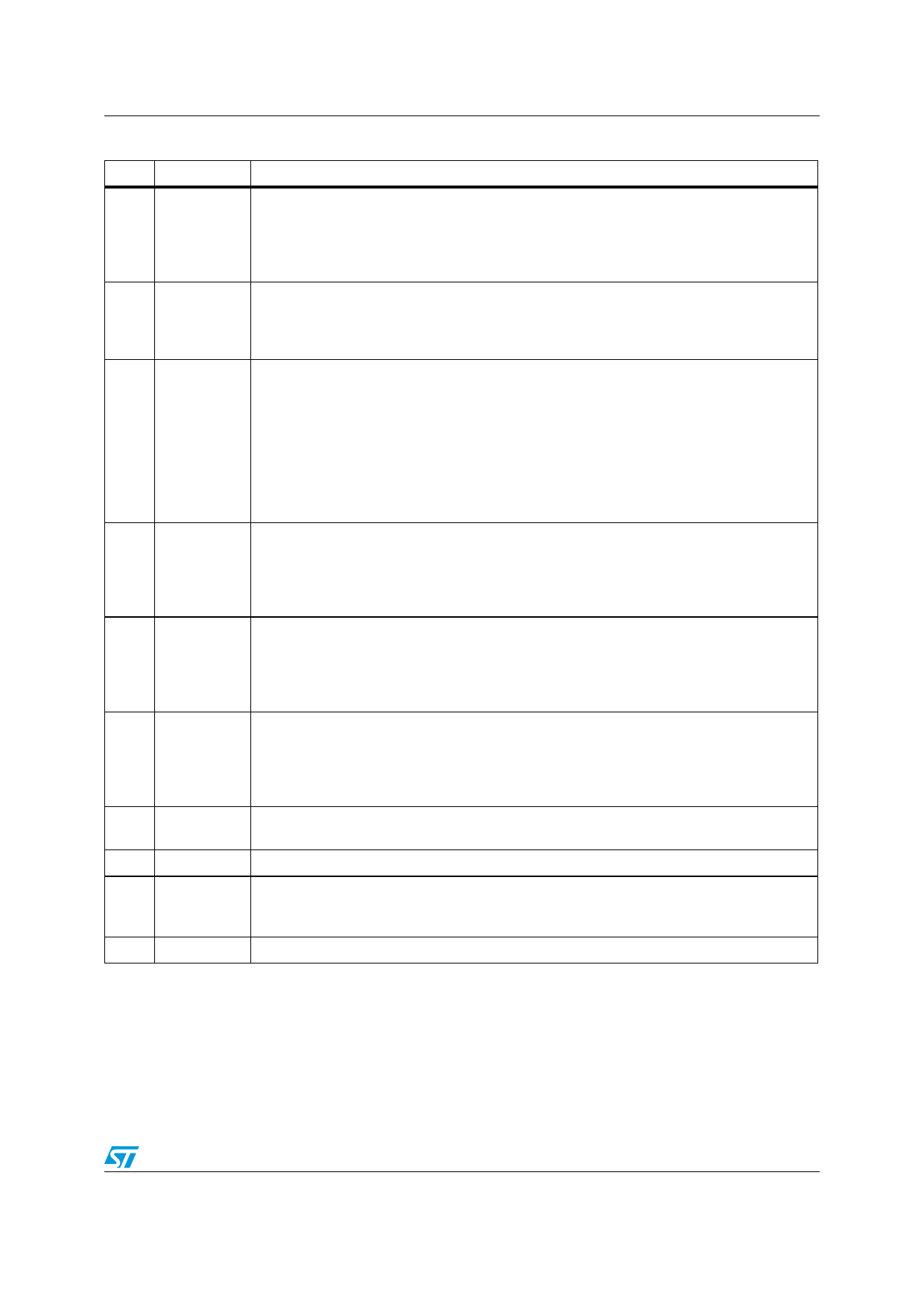

Table 1. Pin description (continued)

Pin N° Name

Description

Inverting input of the error amplifier. The information on the output voltage of the PFC pre-

regulator is fed into the pin through a resistor divider.

1

INV

The pin normally features high impedance but, if the tracking boost function is used, an

internal current generator programmed by TBO (pin 6) is activated. It sinks current from the

pin to change the output voltage so that it tracks the mains voltage.

Tracking Boost function. This pin provides a buffered VFF voltage. A resistor connected

6

TBO

between this pin and GND defines a current that is sunk from pin INV (pin 1). In this way,

the output voltage is changed proportionally to the mains voltage (tracking boost). If this

function is not used leave this pin open.

PFC pre-regulator output voltage monitoring/disable function. This pin senses the output

voltage of the PFC pre-regulator through a resistor divider and is used for protection

purposes. If the voltage at the pin exceeds 2.5V the IC is shut down, its consumption goes

almost to the start-up level and this condition is latched. PWM_LATCH pin is asserted high.

7

PFC_OK Normal operation can be resumed only by cycling the Vcc. This function is used for

protection in case the feedback loop fails.

If the voltage on this pin is brought below 0.2V the IC is shut down and its consumption is

considerably reduced. To restart the IC the voltage on the pin must go above 0.26V. If these

functions are not needed, tie the pin to a voltage between 0.26 and 2.5 V.

Output pin for fault signaling. During normal operation this pin features high impedance. If

either a voltage above 2.5V at PFC_OK (pin 7) or a voltage above 1.7V on CS (pin 4) of

8 PWM_LATCH L6563A is detected the pin is asserted high. Normally, this pin is used to stop the operation

of the DC-DC converter supplied by the PFC pre-regulator by invoking a latched disable of

its PWM controller. If not used, the pin will be left floating.

Output pin for fault signaling. During normal operation this pin features high impedance. If

the IC is disabled by a voltage below 0.5V on RUN (pin 10) the voltage at the pin is pulled

9 PWM_STOP to ground. Normally, this pin is used to temporarily stop the operation of the DC-DC

converter supplied by the PFC pre-regulator by disabling its PWM controller. If not used,

the pin will be left floating.

Remote ON/OFF control. A voltage below 0.52V shuts down (not latched) the IC and

brings its consumption to a considerably lower level. PWM_STOP is asserted low. The IC

10

RUN

restarts as the voltage at the pin goes above 0.6V. Connect this pin to VFF (pin 5) either

directly or through a resistor divider to use this function as brownout (AC mains

undervoltage) protection, tie to INV (pin 1) if the function is not used.

11

ZCD

Boost inductor’s demagnetization sensing input for transition-mode operation. A negative-

going edge triggers MOSFET’s turn-on.

12

GND

Ground. Current return for both the signal part of the IC and the gate driver.

Gate driver output. The totem pole output stage is able to drive power MOSFET’s and

13

GD

IGBT’s with a peak current of 600 mA source and 800 mA sink. The high-level voltage of

this pin is clamped at about 12V to avoid excessive gate voltages.

14

VCC

Supply Voltage of both the signal part of the IC and the gate driver.

5/37