IDT49C465PQF Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Fabricante

IDT49C465PQF Datasheet PDF : 38 Pages

| |||

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

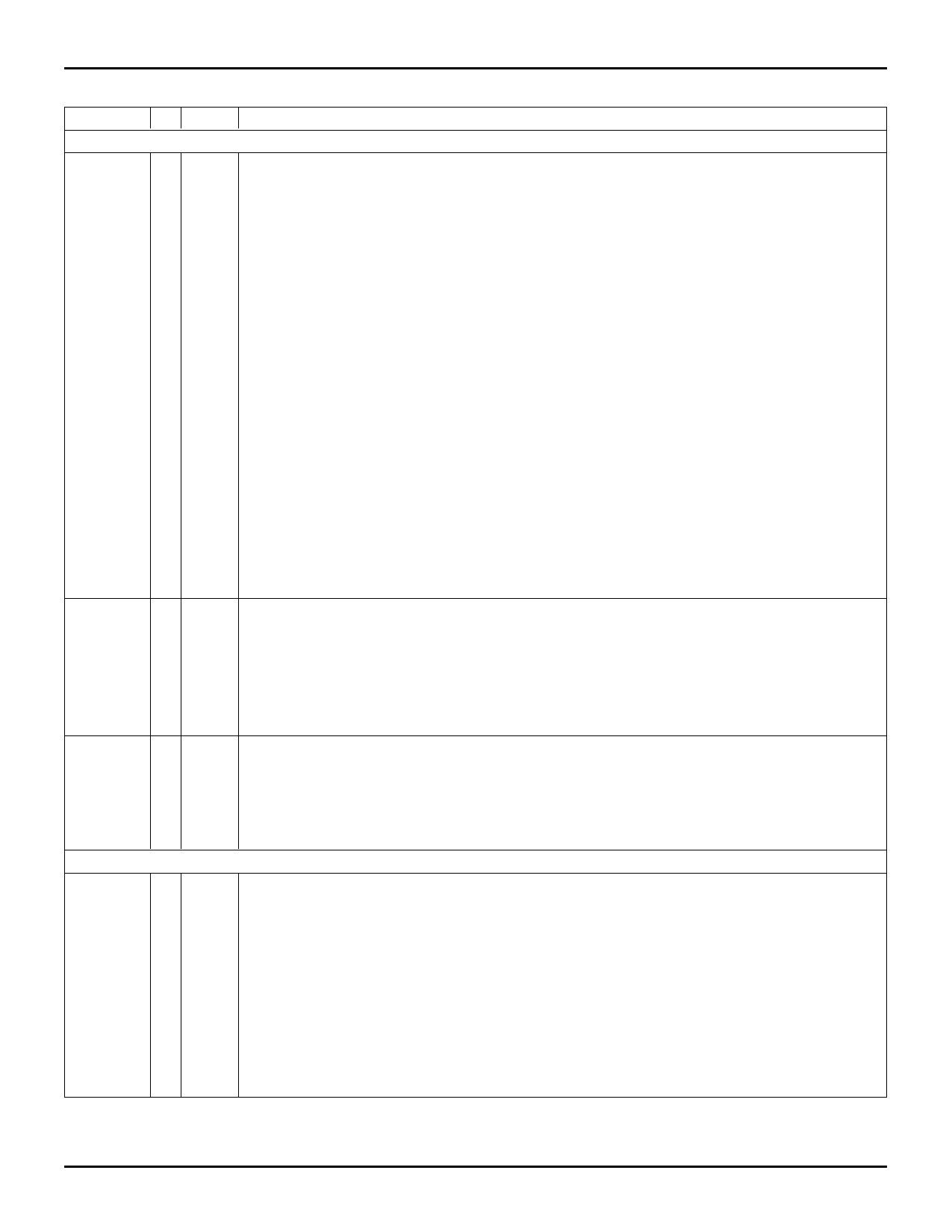

PIN DESCRIPTIONS

Symbol I/O

I/O Buses and Controls

SD0-7

I/O

SD8-15

SD16-23

SD24-31

SLE

I

PLE

I

SOE

I

BE0-3

I

Name and Function

System Data Bus: Data from MD0-31 appears at these pins corrected if MODE 2-0 = x11, or uncor-

rected in the other modes. The BEn inputs must be high and the SOE pin must be low to enable the SD

output buffers during a read cycle. (Also, see diagnostic section.)

Separate I/O memory systems: In a write or partial-write cycle, the byte not-to-be-modified is output on

SDn to n+7 for re-writing to memory, if BEn is high and SOE is low. The new bytes to be written to memory

are input on the SDn pins, for writing checkbits to memory, if BEn is low.

Bi-directional memory systems: In a write or partial-write cycle, the byte not-to-be-modified is re-directed

to the MD I/O pins, if BEn is high, for checkbit generation and rewriting to memory via the MD I/O pins. SOE

must be high to avoid enabling the output drivers to the system bus in this mode. The new bytes to be written

are input on the SDn pins for checkbit generation and writing to memory. BEn must be low to direct input

data from the System Data bus to the MD I/O pins for checkbit generation and writing to the checkbit memory.

System Latch Enable: SLE is an input used to latch data at the SD inputs. The latch is transparent when

SLE is high; the data is latched when SLE is low.

Pipeline Latch Enable: PLE is an input which controls a pipeline latch, which controls data to be output on

the SD bus and the MD bus during byte merges. Use of this latch is optional. The latch is transparent when

PLE is low; the data is latched when PLE is high.

System Output Enable: When low, enables System output drivers and Parity output drivers if correspond-

ing Byte Enable inputs are high.

Byte Enables: In systems using separate I/O memory buses, BEn is used to enable the SD and Parity

outputs for byte n. The BEn pins also control the “Byte mux”. When BEn is high, the corrected or uncorrected

data from the Memory Data latch is directed to the MD I/O pins and used for checkbit generation for byte

n. This is used in partial-word-write operations or during correction cycles. When BEn is low, the data from

the System Data latch is directed to the MD I/O pins and used for checkbit generation for byte n.

BE0 controls SD0-7

BE2 controls SD16-23

BE1 controls SD8-15

BE3 controls SD24-31

MD0-31

I/O

MLE

I

MOE

I

Memory Data Bus: These I/O pins accept a 32-bit data word from main memory for error detection and/

or correction. They also output corrected old data or new data to be written to main memory when the EDC

unit is used in a bi-directional configuration.

Memory Latch Enable: MLE is used to latch data from the MD inputs and checkbits from the CBI inputs.

The latch is transparent when MLE is high; data is latched when MLE is low. When identified as the upper

slice in a 64-bit cascade, the checkbit latch is bypassed.

Memory Output Enable: MOE enables Memory Data Bus output drivers when low.

P0-3

I/O

PSEL

I

Parity I/O: The parity I/O pins for Bytes 0 to 3. These pins output the parity of their respective bytes when

that byte is being output on the SD bus. These pins also serve as parity inputs and are used in generating

the Parity ERRor (PERR) signal under certain conditions (see Byte Enable definition). The parity is odd or

even depending on the state of the Parity SELect pin (PSEL).

Parity SELect: If the Parity SELect pin is low, the parity is even.

If the Parity SELect pin is high, the parity is odd.

Inputs

CBI0-7

I

PCBI 0-7

I

CheckBits-In (00)

CheckBits-In-1 (10)

Partial-Syndrome-In (11):

In a single EDC system or in the lower slice of a cascaded EDC system, these inputs accept the checkbits

from the checkbit memory. In the upper slice in a cascaded EDC system, these inputs accept the “Partial-

Syndrome” from the lower slice (Detect/Correct path).

Partial-CheckBits-In (10)

Partial-CheckBits-In (11):

In a single EDC system, these inputs are unused but should not be allowed to float. In a cascaded EDC

system, the “Partial-Checkbits” used by the lower slice are accepted by these inputs (Correction path only).

In the upper slice of a cascaded EDC system, “Partial-Checkbits” generated by the lower slice are accepted

by these inputs (Generate path).

CODE ID1,0 I

CODE IDentity: Inputs which identify the slice position/ functional mode of the IDT49C465.

(00) Single 32-bit EDC unit

(10) Lower slice of a 64-bit cascade

(01) 64-bit “Checkbit-generate-only” unit

(11) Upper slice of a 64-bit cascade

2552 tbl 01

11.7

7