IDT49C465AG Ver la hoja de datos (PDF) - Integrated Device Technology

Número de pieza

componentes Descripción

Fabricante

IDT49C465AG Datasheet PDF : 38 Pages

| |||

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

FUNCTIONAL DESCRIPTION

The error detection/correction codes consist of a modified

Hamming code; it is identical to that used in the IDT49C460.

32-BIT MODE (CODE ID 1,0=00)

VCC

8

CHECKBITS–IN

7

PCBI

CBI7

CBI0–6

MILITARY AND COMMERCIAL TEMPERATURE RANGES

CHECKBITS–OUT

CBO

7

SYO

7 SYNDROME–OUT

EDC

2552 drw 09

Figure 5. 32-Bit Mode

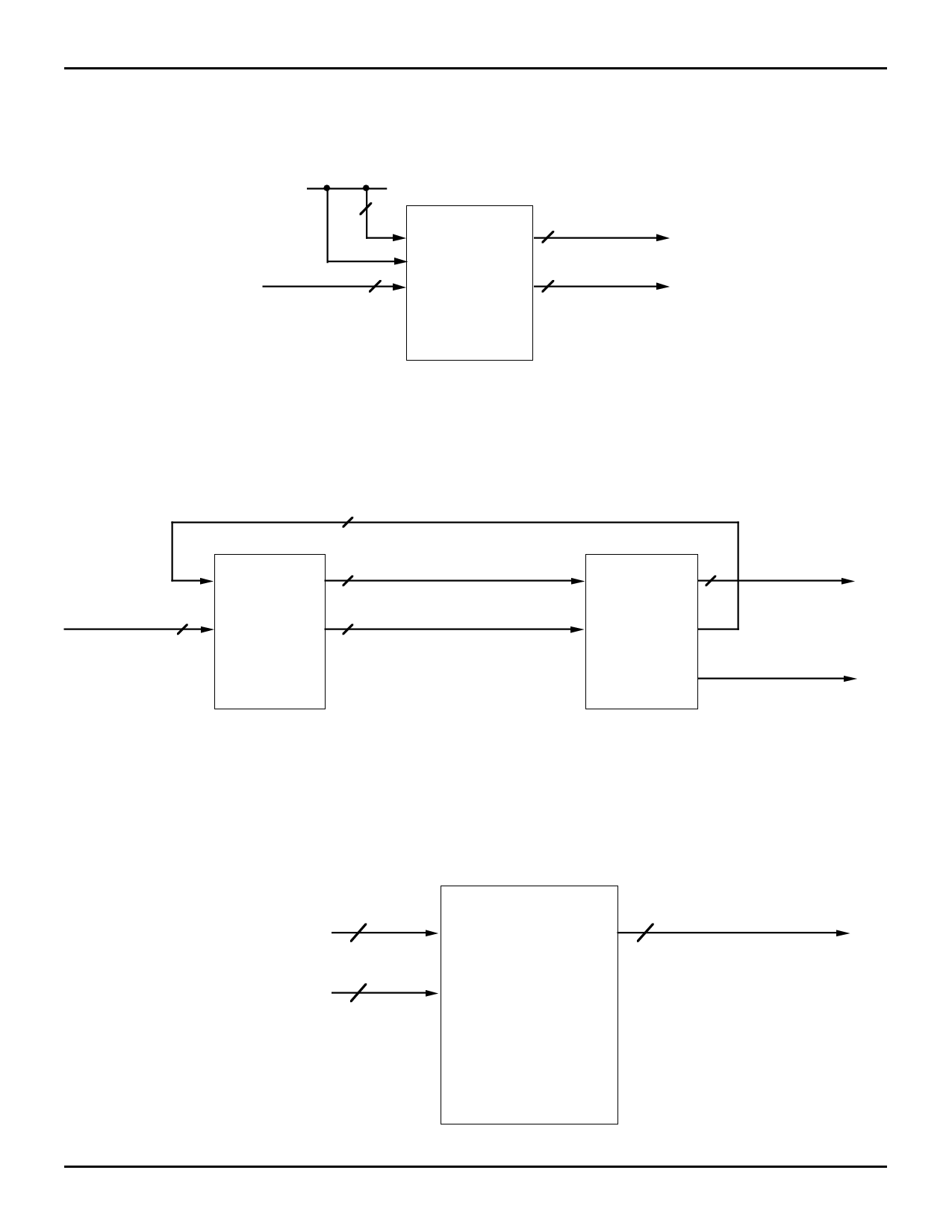

64-BIT MODE (CODE ID 1,0=10 & 11)

The expansion bus topology is shown in Figure 6. This

topology allows the syndrome bits used by the correction logic

to be generated simultaneously in both parts used in the

expansion. During a 64-bit detection or correction operation,

“Partial-Checkbit” data and “Partial-Syndrome” data is simul-

taneously exchanged between the two EDC units in opposite

directions on dedicated expansion buses. This results in very

short 64-bit detection and correction times.

8 PARTIAL–CHECKBITS–OUT (11)

(CORRECTION ONLY)

PCBI

CBO

PCBI

8 PARTIAL–CHECKBITS–OUT (10)

(GENERATE ONLY)

CBO

8

FINAL

CHECKBITS–OUT

CBI

SYO

CBI

SYO

CHECKBITS–IN 8

8 PARTIAL–SYNDROME

(DETECT/CORRECT ONLY)

LOWER EDC

ERR

UPPER EDC

(DETECT AND CORRECT)

(CODE ID 1,0 = 10)

(CODE ID 1,0 = 11)

2552 drw 10

Figure 6. 64-Bit Mode — 2 Cascaded IDT49C465 Devices

64-BIT GENERATE-ONLY MODE (CODE ID 1,0=01)

If the Identity pins CODE ID 1,0 = 01, a single EDC is placed

in the 64-bit “Generate-only” mode. In this mode, the lower 32

bits of the 64-bit data word enter the device on the MD0-31

inputs and the upper 32-bits of the 64 bit data word enter the

device on the SD0-31 inputs. This provides the device with the

full 64-bit word from memory. The resultant generated

checkbits are output on the CBO0-7 outputs. The generate

time is less than that resulting from using a 2-chip cascade.

LOWER 32 BITS (0–31)

UPPER 32 BITS (32–63)

MD0–31

CBO

32

8

CHECKBITS–OUT

SD0–31

32

EDC

Figure 7. 64-Bit "Generate-Only" Mode (Single Chip)

11.7

2552 drw 11

6