TTSI4K32T3BAL Ver la hoja de datos (PDF) - Agere -> LSI Corporation

Número de pieza

componentes Descripción

Fabricante

TTSI4K32T3BAL Datasheet PDF : 64 Pages

| |||

TTSI4K32T

4096-Channel, 32-Highway Time-Slot Interchanger

Data Sheet

June 2000

Functional Description (continued)

The device capabilities include several test features for board and device diagnostics.

s Test-pattern checking on input time slots (PRBS, QRSS, or a fixed byte).

s Test-pattern generation on output time slots (PRBS, QRSS, or a fixed byte).

s JTAG on all I/O.

s Software-controlled BIST of data store and connection store memory.

s TEST pin for isolating the TTSI4K32T during board test.

The microprocessor interface supports two modes of operation, synchronous and asynchronous. These modes are

selected based on the MM input pin. Both modes provide an 8-bit demultiplexed address and data bus. Fifteen

address pins allow direct access to the 32 Kbyte address space. This interface provides direct access to the control

registers and data store and connection store memories.

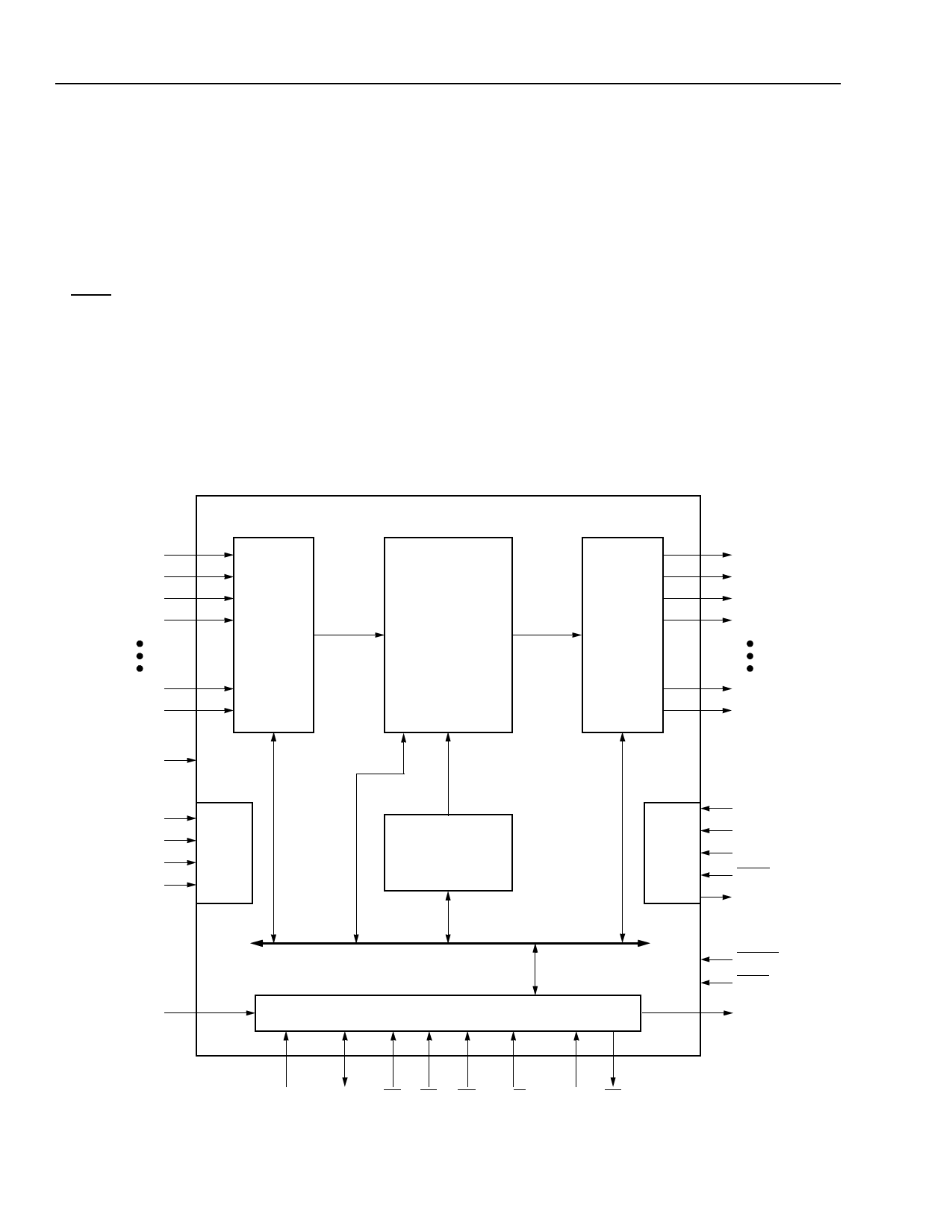

The TTSI4K32T is fabricated using a low-power, high-density, CMOS process that nominally operates at 3.3 V with

TTL switching thresholds and 5 V tolerance on the inputs and outputs. A basic block diagram of the architecture is

shown in Figure 1.

RXD0

RXD1

RXD2

RXD3

RXD30

RXD31

FSYNC

CK

CKSPD0

CKSPD1

CKSPD2

RECEIVE

HIGHWAYS

TDM

DATA

DATA

STORE

TDM

DATA

TRANSMIT

HIGHWAYS

PLL

AND

CK

LOGIC

DATA STORE

ADDRESS

CONNECTION

STORE

JTAG

TXD0

TXOE0

TXD1

TXOE1

TXD31

TXOE31

TCK

TDI

TMS

TRST

TDO

HOST ADDRESS/DATA BUS

MM

MICROPROCESSOR INTERFACE

RESET

TEST

INT

A[14—0] D[7—0] CS AS DS R/W

PCLK DT

5-5780(F).br.1

Figure 1. Block Diagram of the TTSI4K32T

6

Lucent Technologies Inc.