HM628128A Ver la hoja de datos (PDF) - Hitachi -> Renesas Electronics

NГәmero de pieza

componentes DescripciГіn

Fabricante

HM628128A Datasheet PDF : 13 Pages

| |||

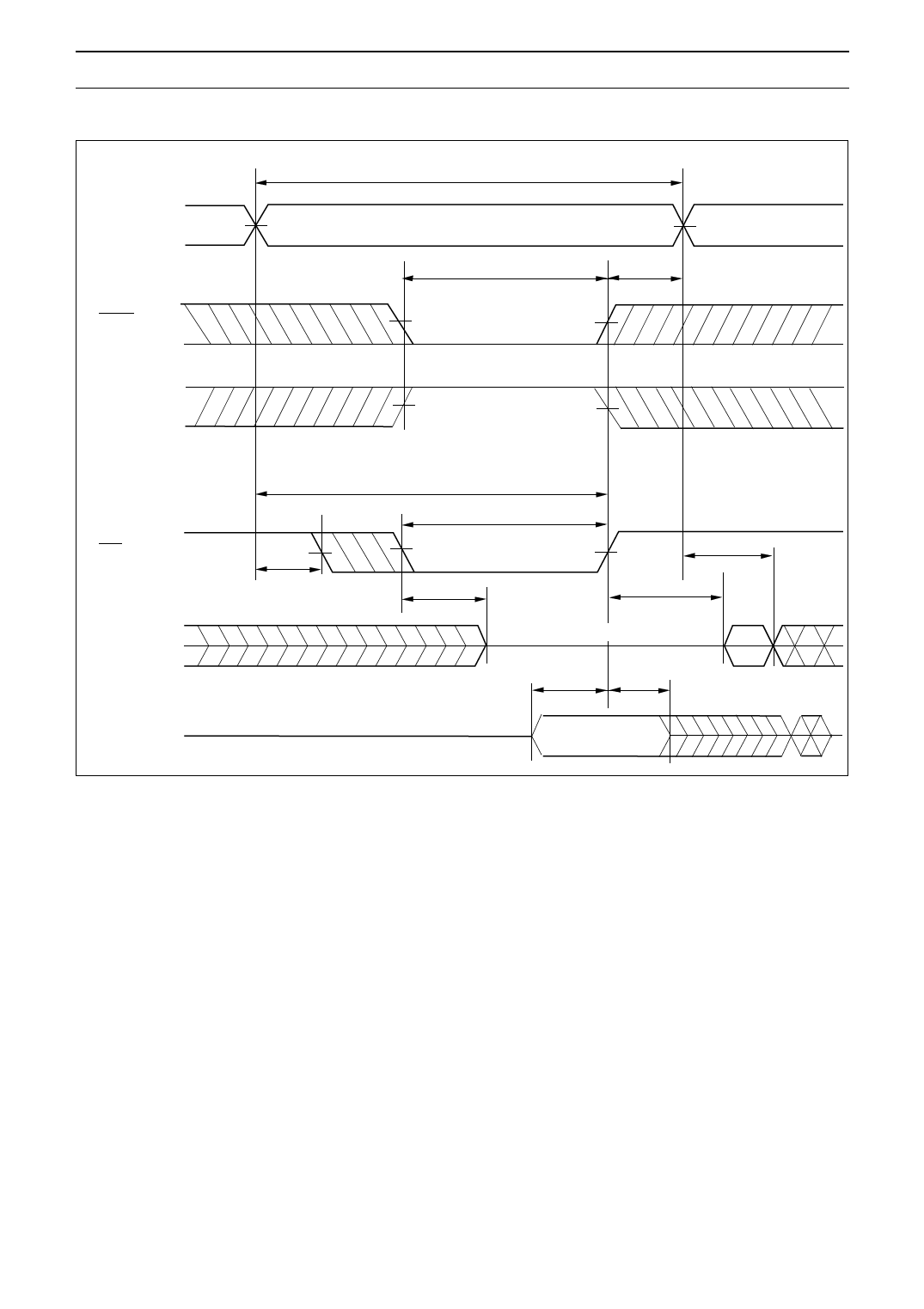

Write Timing Waveform (2) (OE low Fixed)

t WC

Address

Address Valid

t CW *2

CS1

*6

HM628128A Series

t

*4

WR

CS2

WE

Dout

Din

t AS *3

t AW

t WP *1 *11

t OH

t WHZ *5

t OW

High Impedance

*7

*8

t DW

t DH

*9

Data Valid

Notes: 1. A write occurs during the overlap of a low CS1, a high CS2, and a low WE. A write begins at the

latest transition among CS1 going low, CS2 going high, and WE going low. A write ends at the

earliest transition among CS1 going high, CS2 going low, and WE going high. tWP is measured

from the beginning of write to the end of write.

2. tCW is measured from the later of CS1 going low or CS2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the earliest of CS1 or WE going high or CS2 going low to the end of write

cycle.

5. During this period, I/O pins are in the output state; therefore, the input signals of the opposite

phase to the outputs must not be applied.

6. If the CS1 goes low simultaneously with WE going low or after the WE going low, the outputs

remain in a high impedance state.

7. Dout is the same phase of the latest written data in this write cycle.

8. Dout is the read data of next address.

9. If CS1 is low and CS2 high during this period, I/O pins are in the output state. Therefore, the

input signals of opposite phase to the outputs must not be applied to them.

10. This parameter is sampled and not 100% tested.

11. In the write cycle with OE low fixed, tWP must satisfy the following equation to avoid a problem of

11