HIP0063AB Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

Fabricante

HIP0063AB Datasheet PDF : 8 Pages

| |||

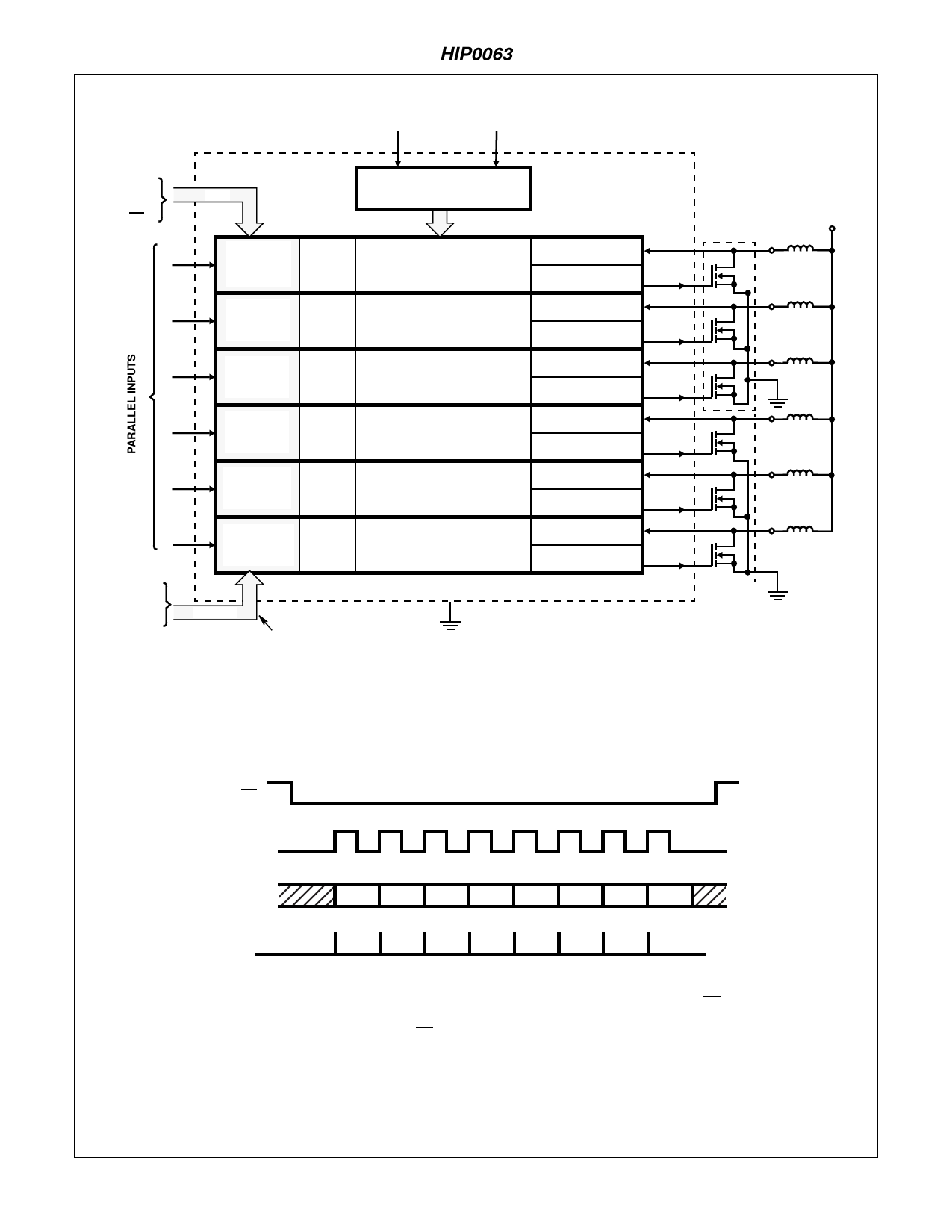

HIP0063

VCC

5V

VPWR

14V

S0

SI

SPI

SCK

CS

PARALLEL/

PI0

SERIAL IN, DATA

SHIFT REG. LATCH

CONTROL

PARALLEL/

PI1

SERIAL IN,

DATA

SHIFT REG. LATCH

CONTROL

PARALLEL/

PI2

SERIAL IN,

DATA

SHIFT REG. LATCH

CONTROL

PARALLEL/

PI3

SERIAL IN,

DATA

SHIFT REG. LATCH

CONTROL

PARALLEL/

PI4

SERIAL IN,

DATA

SHIFT REG. LATCH

CONTROL

PARALLEL/

PI5

SERIAL IN,

DATA

SHIFT REG. LATCH

CONTROL

POR, TIMING OSC,

BAND GAP REF.,

OVER-VOLT. DET.

DRIVE CONTROL

CHANNEL #0

DRIVE CONTROL

CHANNEL #1

DRIVE CONTROL

CHANNEL #2

DRIVE CONTROL

CHANNEL #3

DRIVE CONTROL

CHANNEL #4

DRIVE CONTROL

CHANNEL #5

HLOS (SEL)

HPW01

HPW45

HLOS

GND

HARDWARE GENERATED OR CUSTOM LOGIC

SOURCED PWM CONTROL SIGNAL INPUTS

D0

DRAIN MONITOR

GATE DRIVER

DRAIN MONITOR

G0

D1

GATE DRIVER

DRAIN MONITOR

G1

D2

GATE DRIVER

DRAIN MONITOR

G2

D3

GATE DRIVER

DRAIN MONITOR

G3

D4

GATE DRIVER

DRAIN MONITOR

G4

D5

GATE DRIVER G5

VPWR (VBATT)

14V

HIP0063

2 - HIP0061

OR EQUIVALENT

FIGURE 1. TYPICAL APPLICATION CIRCUIT FOR THE HIP0063 SHOWING HOW THE GATE DRIVE OUTPUT AND DRAIN MONITOR

INPUT CONTROLS TWO HIP0061 THREE FET ARRAYS

CS

SCK

(CPOL = 0, CPHA = 1)

MSB

6

5

4

3

2

1

LSB

INTERNAL STROBE FOR DATA CAPTURE

FIGURE 2. SPI DATA AND CLOCK TIMING DIAGRAM. SERIAL COMMUNICATION IS INITIATED WHEN CS GOES LOW AND SCK

IS LOW. 8 OR 16 BITS OF DATA IS CLOCKED INTO SI ON THE LEADING EDGE OF SCK. DATA IS CLOCKED OUT OF

SO ON THE TRAIL EDGE OF SCK. WHEN CS GOES HIGH, DATA IS LATCHED TO CONTROL EACH CHANNEL

2