EPL09060GH Ver la hoja de datos (PDF) - ELAN Microelectronics

Número de pieza

componentes Descripción

Fabricante

EPL09060GH Datasheet PDF : 54 Pages

| |||

EPL09060

9 COM/60 SEG LCD Driver

Parallel Interface (8-bit Length)

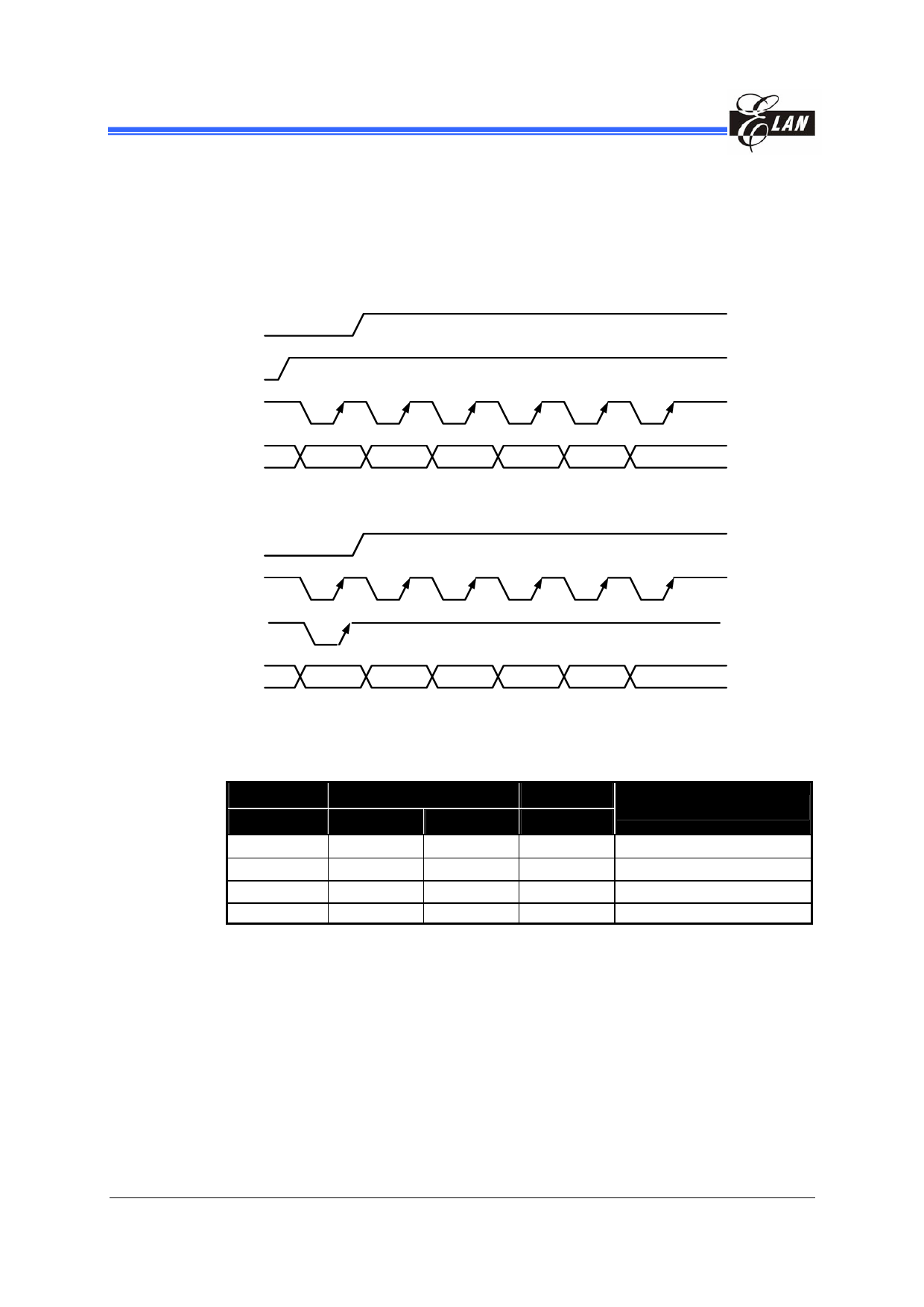

Parallel mode (8-bit length): When parallel input is selected (PS = ”H”), D0~D7 can be

connected directly to the 80-series or 68-series MPU by setting the C86 pin to high or

low.

A0

/RD

/WR

D7~D0

A0

/RD

/WR

D7~D0

N

D(N)

D(N+1)

D(N+2)

D(N+3)

D(N+4)

Write Timing Diagram

N

Dummy

D(N)

D(N+1)

D(N+2)

Read Timing Diagram

Figure 5 Write and Read Timing Diagrams

D(N+3)

Common

A0

H

H

L

L

80-Series

/RD

/WR

L

H

H

L

L

H

H

L

68-Series

R/W

H

L

H

L

Description

Display data read

Display data write

Register status read

Writes to Instruction register

7.2 Data Transfer

The EPL09060 uses a bus holder and an internal data bus for data transfer with the

MPU. When writing data from the MPU to the DDRAM, data is automatically

transferred from the bus holder to the DDRAM. When reading data from the DDRAM

to the MPU, the data for the initial read cycle is stored in the bus holder (dummy read)

and the MPU reads this stored data from the bus holder for the next data read cycle.

14 •

Product Specification (V1.0) 12.28.2005