EM78P142SS10J/S Ver la hoja de datos (PDF) - ELAN Microelectronics

Número de pieza

componentes Descripción

Fabricante

EM78P142SS10J/S Datasheet PDF : 96 Pages

| |||

EM78P142

8-Bit Microprocessor with OTP ROM

6 Function Description

6.1 Operational Registers

6.1.1 R0 (Indirect Address Register)

R0 is not a physically implemented register. It is used as an indirect address pointer.

Any instruction using R0 as a pointer, actually accesses the data pointed by the RAM

Select Register (R4).

6.1.2 R1 (Time Clock)

Incremented by the instruction cycle clock.

Writable and readable as any other registers.

The TCC prescaler counter (IOCC1) is assigned to TCC

The contents of the IOCC1 register is cleared whenever –

• a value is written to the TCC register.

• a value is written to the TCC prescaler bits (Bits 3, 2, 1, 0 of the CONT register)

• there is power-on reset, /RESET, or WDT time out reset.

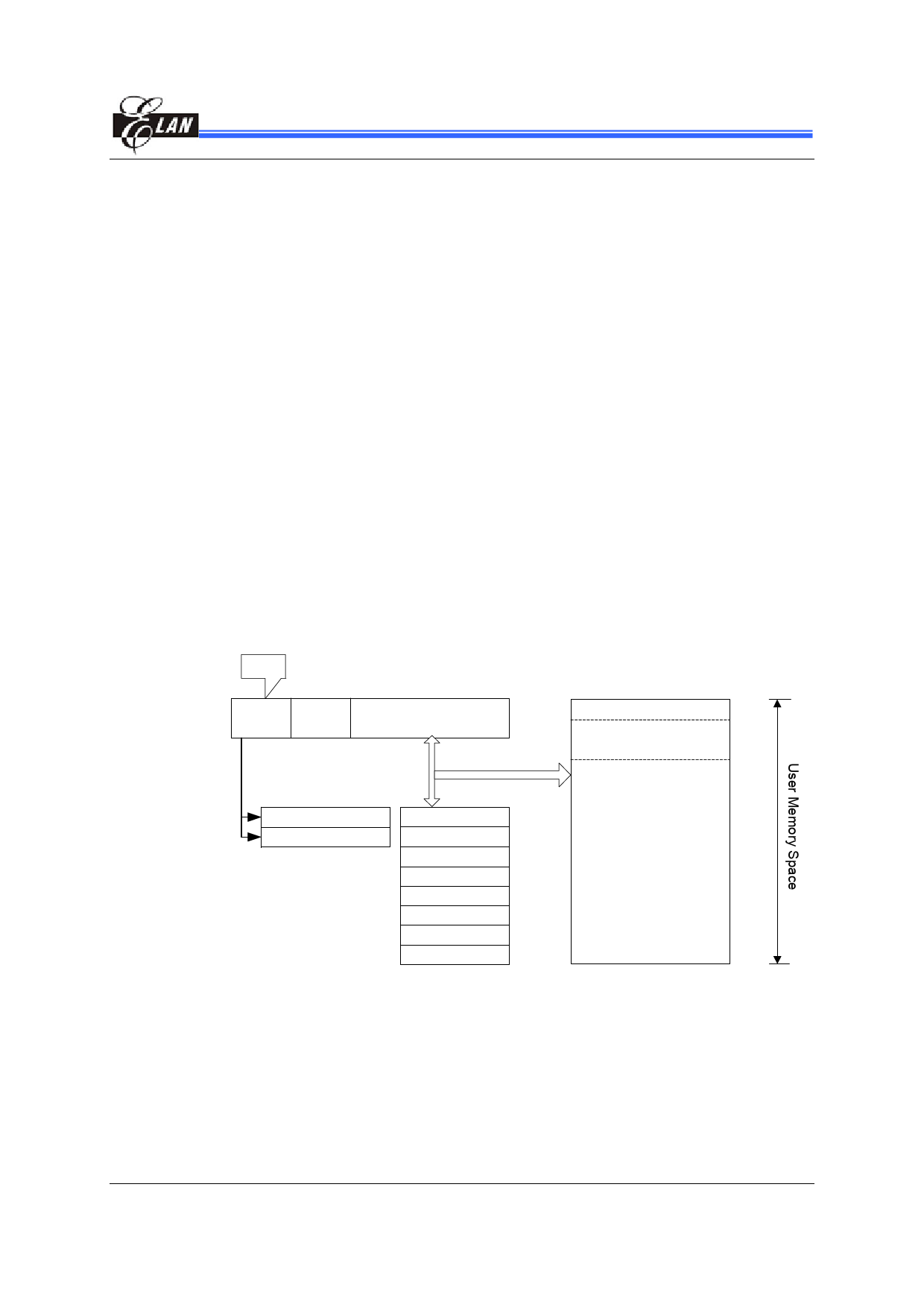

6.1.3 R2 (Program Counter) and Stack

R3

A10 A9 A8

A7 ~ A0

CALL

RET

RETL

RETI

0 PAGE0 0000~03FF Stack Level 1

1 PAGE1 0400~07FF Stack Level 2

Stack Level 3

Stack Level 4

Stack Level 5

Stack Level 6

Stack Level 7

Stack Level 8

Reset Vector

Hardware Interrupt Vector

000H

003H

~

021H

On-chip Program

Memory

7FFH

Figure 6-1 Program Counter Organization

R2 and hardware stacks are 11-bit wide. The structure is depicted in the table

under Section 6.1.3.1 Data Memory Configuration.

The configuration structure generates 2K×13 bits on-chip ROM addresses to the

relative programming instruction codes. One program page is 1024 words long.

The contents of R2 are all set to "0"s when a reset condition occurs.

Product Specification (V1.0) 01.25.2008

•5

(This specification is subject to change without further notice)