DP805X Ver la hoja de datos (PDF) - Digital Core Design

Número de pieza

componentes Descripción

Fabricante

DP805X Datasheet PDF : 79 Pages

| |||

DP805x Instructions set details

-6-

1. OVERVIEW

1.1. DOCUMENT STRUCTURE.

Document contains brief description of DP805X instructions. This manual is intended

for design engineers who are planning to use the DP805X HDL core in conjunction with

software assembler, compiler and debugger tools.

2. INSTRUCTIONS SET BRIEF

2.1. INSTRUCTION SET NOTES

The DP805X has five different addressing modes: immediate, direct, register, indirect

and relative. In the immediate addressing mode the data is contained in the opcode. By

direct addressing an eight bit address is a part of the opcode, by register addressing, a

register is selected in the opcode for the operation. In the indirect addressing mode, a

register is selected in the opcode to point to the address used by the operation. The

relative addressing mode is used for jump instructions.

The following tables give a survey about the instruction set cycles of the DP805X

microcontroller core. One cycle is equal to one clock period.

Table 1 and Table 2 contain notes for mnemonics used in Instruction set tables. Tables 3 -

7 show instruction hexadecimal codes, number of bytes and machine cycles that each

instruction takes to execute.

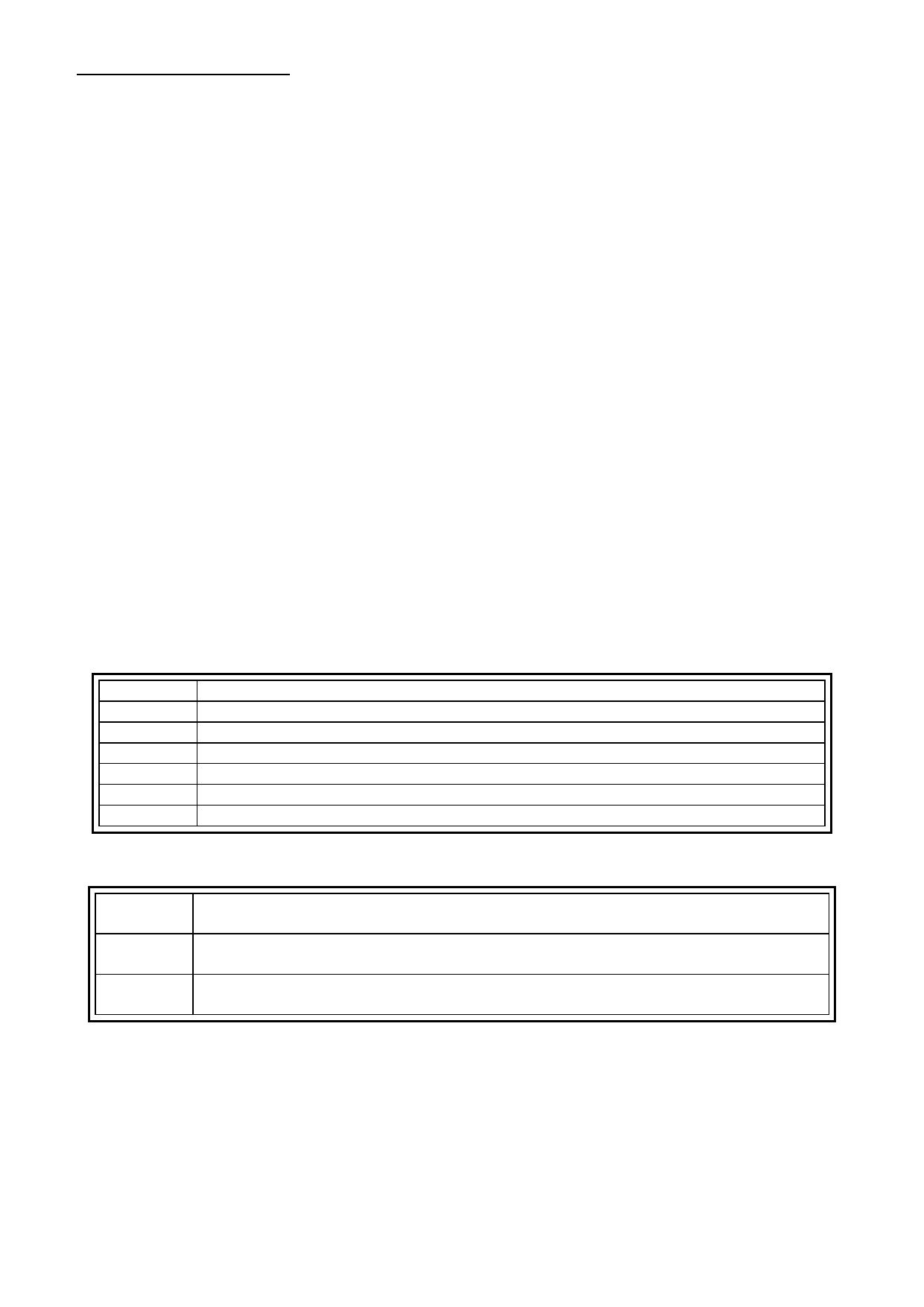

Rn

direct

@Ri

#data

#data16

bit

A

Working register R0-R7

128 internal RAM locations, any Special Function Registers

Indirect internal or external RAM location addressed by register R0 or R1

8-bit constant included in instruction

16-bit constant included as bytes 2 and 3 of instruction

256 software flags, any bit-addressable l/O pin, control or status bit

Accumulator

Table 1. Notes on data addressing modes

addr16

addr11

rel

Destination address for LCALL and LJMP may be anywhere within the 64-Kbyte of

program memory address space.

Destination address for ACALL and AJMP will be within the same 2-Kbyte page of

program memory as the first byte of the following instruction.

SJMP and all conditional jumps include an 8-bit offset byte. Range is +127/-128

bytes relative to the first byte of the following instruction

Table 2. Notes on program addressing modes

All trademarks mentioned in this document

are trademarks of their respective owners.

http://www.DigitalCoreDesign.com

http://www.dcd.pl

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.