DD28F032SA Ver la hoja de datos (PDF) - Intel

Número de pieza

componentes Descripción

Fabricante

DD28F032SA Datasheet PDF : 49 Pages

| |||

E

DD28F032SA

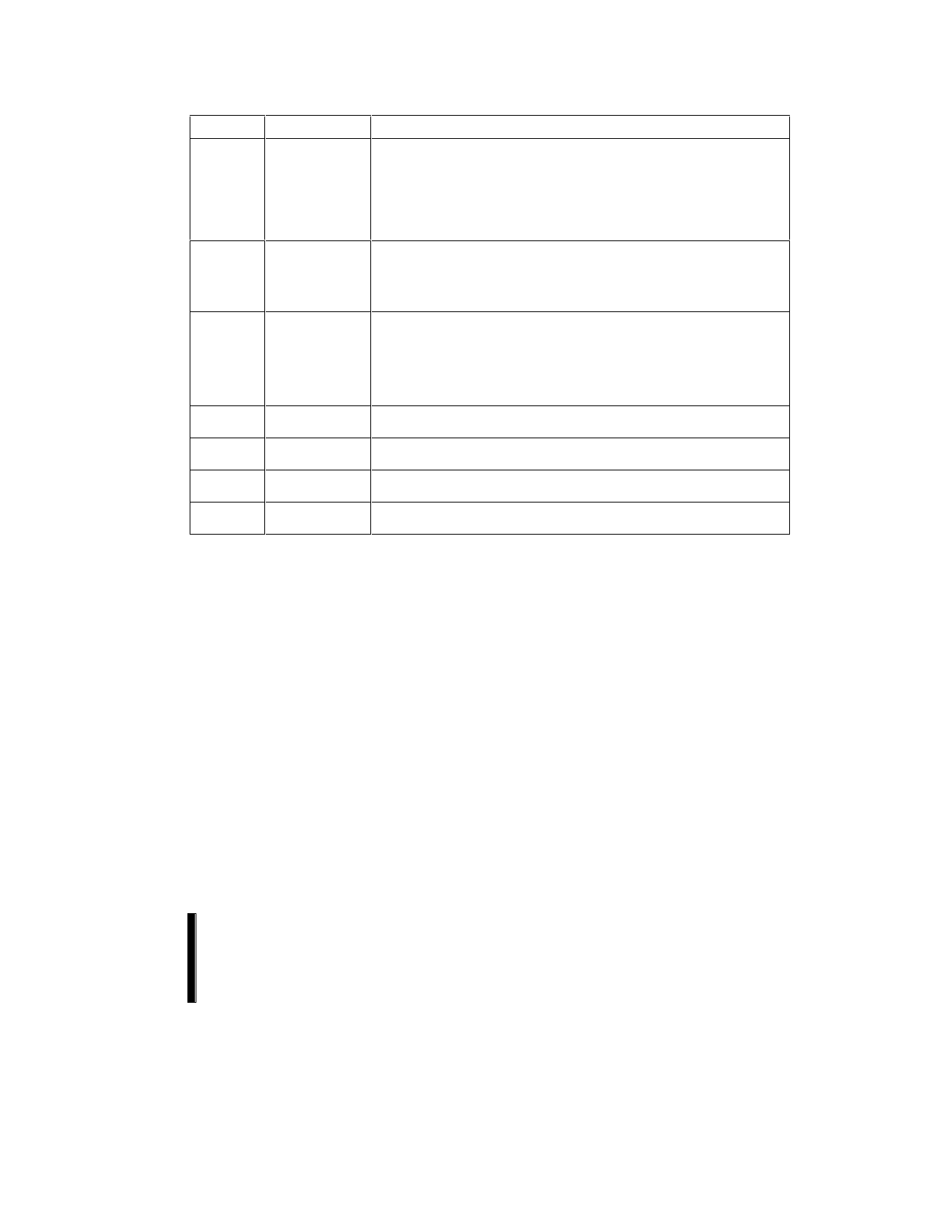

2.1 Lead Descriptions (Continued)

Symbol

WP#

BYTE#

3/5#

VPP

VCC

GND

NC

Type

INPUT

INPUT

INPUT

SUPPLY

SUPPLY

SUPPLY

Name and Function

WRITE PROTECT: Erase blocks can be locked by writing a nonvolatile

lock-bit for each block. When WP# is low, those locked blocks as

reflected by the Block-Lock Status bits (BSR.6), are protected from

inadvertent data programs or block erases. When WP# is high, all blocks

can be written or erased regardless of the state of the lock-bits. The WP#

input buffer is disabled when RP# transitions low (deep power-down

mode).

BYTE ENABLE: BYTE# low places device in x8 mode. All data is then

input or output on DQ0-7, and DQ8-15 float. Address A0 selects between

the high and low byte. BYTE# high places the device in x16 mode, and

turns off the A0 input buffer. Address A1 then becomes the lowest order

address.

3.3/5.0 VOLT SELECT: 3/5# high configures internal circuits for 3.3V

operation. 3/5# low configures internal circuits for 5.0V operation.

NOTES:

Reading the array with 3/5# high in a 5.0V system could damage the

device.

There is a significant delay from 3/5# switching to valid data.

ERASE/PROGRAM POWER SUPPLY: For erasing memory array blocks

or writing words/bytes/pages into the flash array.

DEVICE POWER SUPPLY (3.3V ± 0.3V, 5.0V ± 0.5V, 5.0V ± 0.25V):

Do not leave any power pins floating.

GROUND FOR ALL INTERNAL CIRCUITRY:

Do not leave any ground pins floating.

NO CONNECT:

Lead may be driven or left floating.

9