CY22801 Ver la hoja de datos (PDF) - Cypress Semiconductor

Número de pieza

componentes Descripción

Fabricante

CY22801 Datasheet PDF : 7 Pages

| |||

CY22801

General Description

The CY22801 is a flash-programmable clock generator that

supports various applications in consumer and communications

markets. The device uses a Cypress proprietary PLL to drive up

to three configurable outputs in an 8-pin SOIC.

The CY22801 is programmed with an easy-to-use programmer

dongle, the CY36800, in conjunction with the CyClocksRT™

software. This enables fast sample generation of prototype

builds for user-defined frequencies.

Field Programming the CY22801

The CY22801 is programmed using the CY36800 USB

programmer dongle. The CY22801 is flash-technology based, so

the parts are reprogrammed up to 100 times. This enables fast

and easy design changes and product updates, and eliminates

any issues with old and out-of-date inventory.

Samples and small prototype quantities are programmed using

the CY36800 programmer. Cypress’s value added distribution

partners and third party programming systems from BP

Microsystems, HiLo Systems, and others, are available for large

production quantities.

CyClocksRT Software

CyClocksRT is an easy-to-use software application that enables

the user to custom-configure the CY22801. Users can specify

the XIN/CLKIN frequency, crystal load capacitance, and output

frequencies. CyClocksRT then creates an industry standard

JEDEC file, which is used to program the CY22801.

When needed, an advanced mode is available that enables

users to override the automatically generated VCO frequency

and output divider values.

CyClocksRT is a component of the CyberClocks™ software,

which is downloaded free of charge from the Cypress website at

http://www.cypress.com.

CY36800 InstaClock™ Kit

The Cypress CY36800 InstaClock Kit comes with everything

needed to design the CY22801 and program samples and small

prototype quantities. The CyClocksRT software is used to

quickly create a JEDEC programming file, which is then

downloaded directly to the portable programmer that is included

in the CY36800 InstaClock Kit. The JEDEC file can also be

saved for use in a production programming system for larger

volumes.

The CY36800 also comes with five samples of the CY22800,

which are programmed with preconfigured JEDEC files using the

InstaClock software.

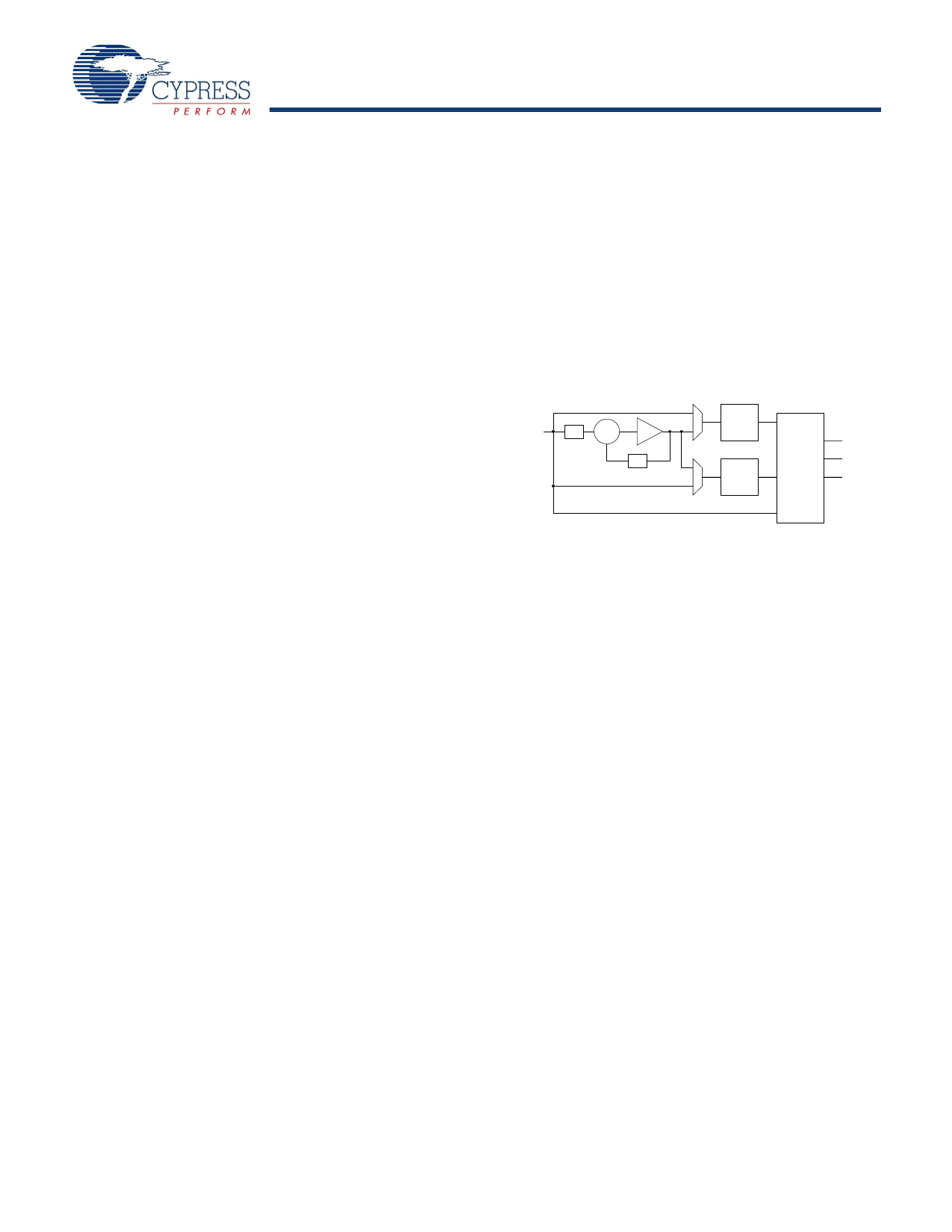

Output Clock Frequencies

The CY22801 is a very flexible clock generator with up to three

individual outputs, generated from an integrated PLL. Details are

shown in Figure 2.

The output of the PLL runs at high frequency and is divided down

to generate the output clocks. Two programmable dividers are

available for this purpose. Thus, although the output clocks may

be different frequencies, they must be related, based on the PLL

frequency.

It is also possible to direct the reference clock input to any of the

outputs, thereby bypassing the PLL. Lastly, the reference clock

may be passed through either divider.

Figure 2. Basic PLL Block Diagram

REF

(XIN/CLKIN)

/Q PFD

VCO

/P

Post

Divider

1N

Post

Divider

2N

Crosspoint

Switch

Matrix

CLKA

CLKB

CLKC

Reference Crystal Input

The input crystal oscillator of the CY22801 is an important

feature because of the flexibility it allows the user in selecting a

crystal as a reference clock source. The oscillator inverter has

programmable gain, enabling maximum compatibility with a

reference crystal, based on manufacturer, process, perfor-

mance, and quality.

Input load capacitors are placed on the CY22801 die to reduce

external component cost. These capacitors are true

parallel-plate capacitors, designed to reduce the frequency shift

that occurs when nonlinear load capacitance is affected by load,

bias, supply, and temperature changes.

The value of the input load capacitors is determined by eight bits

in a programmable register. Total load capacitance is determined

by the formula:

CapLoad = (CL – CBRD – CCHIP)/0.09375 pF

In CyClocksRT, enter the crystal capacitance (CL). The value of

CapLoad is determined automatically and programmed into the

CY22801.

Applications

Controlling Jitter

Jitter is defined in many ways, including:

■ Phase noise

■ Long-term jitter

■ Cycle-to-cycle jitter

■ Period jitter

■ Absolute jitter

■ Deterministic jitter

Document #: 001-15571 Rev. *B

Page 2 of 7

[+] Feedback