CY22801KSXC-XXX(2011) Ver la hoja de datos (PDF) - Cypress Semiconductor

Número de pieza

componentes Descripción

Fabricante

CY22801KSXC-XXX Datasheet PDF : 23 Pages

| |||

CY22801

Spread Percentage

The percentage of spread can be programmed from ±0.25% to

±2.5% for center spread and from –0.5% to –5.0% for down

spread. The granularity is 0.25%.

Modulation Frequency

The default modulation frequency is 31.5 kHz. Other modulation

frequencies available through configuration software are

30.1 kHz and 32.9 kHz.

SSON Pin

SSON pin functionality can be used to turn Spread ON and OFF

in clock output. Any one of the Multifunction pins can be

configured as SSON pin.

Multifunction Pins

There are three pins with multiple functions either as control pins

or as output pins. The following are the acronyms used for the

different control function pins:

■ Output enable (OE): If OE = 1, all outputs are enabled

■ Frequency select (FS0,1,2): These pins can be used to select

one of the programmed clock frequencies for clock output. All

of three multifunction pins support this functionality. Any of

these pins can also be configured as Spread spectrum ON

(SSON) pin. If SSON = 1, clock output has programmed

spread;

if SSON = 0, clock output does not have spread.

■ Power-down: active low (PD#): If PD# = 0, all outputs are

tristated and the device enters in the low-power state

■ Voltage controlled crystal oscillator (VCXO): Analog voltage on

this pin controls the output frequency of oscillator

■ Serial interface clock line (SCLK) and serial interface data line

(SDAT): These pins are for serial interface and are compatible

with I2C.

Each of these three multi-function pins supports selected

functions mentioned in Table 2. One of the supported functions

can be programmed on the pin at a time.

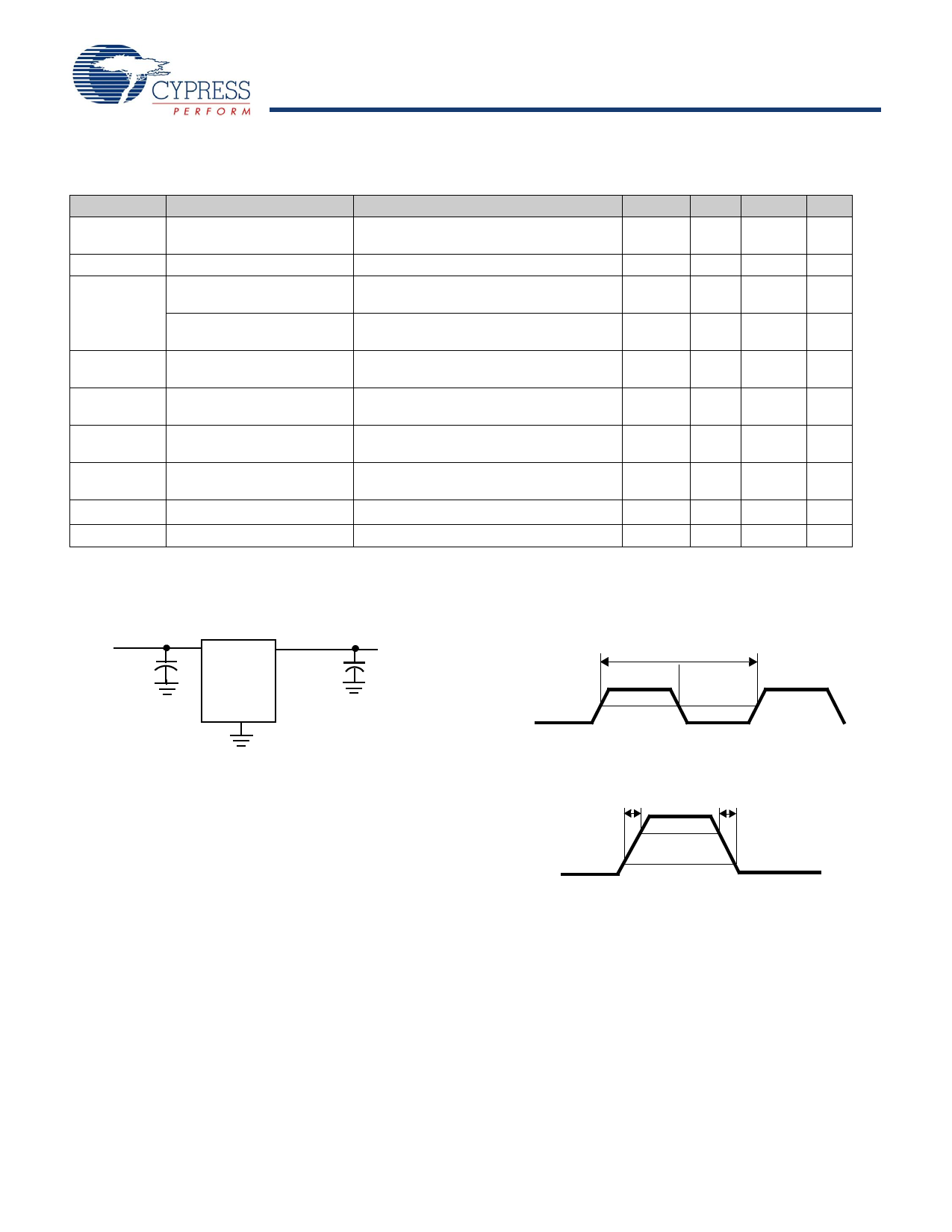

Table 2. Multi Function Pin Options

Pin#

Pin Name

OE

PD#

VCXO

FS

CLK

OUTPUT

I2C

3 SDAT/FS0 Y

/VCXO/OE

/PD#

Y

Y[1] Y[2]

N[3] SDAT

[1]

5 CLKB/FS1/ N N

SCLK

NY

Y SCLK

Table 2. Multi Function Pin Options

Pin#

Pin Name

OE

PD#

VCXO

FS

CLK

OUTPUT

I2C

7 CLKC/FS2 N N

NY

Y[4]

N

Table 3. Possible Combinations for Multifunction Pins

Possible Combinations Pin#3 Pin#5 Pin#7

A

FS0

CLKB CLKC

B

FS0

CLKB

FS2

C

FS0

FS1

FS2

D

OE/PD# CLKB CLKC

E

OE/PD# FS1 CLKC

F

OE/PD# FS1

FS2

G

SDAT SCLK CLKC

H

VCXO CLKB CLKC

Frequency Calculation and Register

Definitions

The CY22801 is an extremely flexible clock generator with four

basic variables that are used to determine the final output

frequency. They are the input reference frequency (REF), the

internally calculated P and Q dividers, and the post divider, which

can be a fixed or calculated value. There are three formulas to

determine the final output frequency of a CY22801 based

design:

■ CLK = ((REF x P)/Q) / Post divider

■ CLK = REF / Post divider

■ CLK = REF.

The basic PLL block diagram is shown in Figure 4. Each of the

three clock outputs on the CY22801 has a total of seven output

options available to it. There are six post divider options

available: /2 (two of these), /3, /4, /DIV1N and /DIV2N. DIV1N

and DIV2N are independently calculated and are applied to

individual output groups. The post divider options can be applied

to the calculated VCO frequency ((REF*P)/Q) or to the REF

directly.

In addition to the six post divider output options, the seventh

option bypasses the PLL and passes the REF directly to the

crosspoint switch matrix.

Notes

1. VCXO and SSON functions as well as VCXO and Serial Interface functions are not compatible.

2. ‘Y’ means pin supports this function.

3. ‘N’ means pin does not support this function.

4. Do not use this pin as Reference Clock Output.

Document #: 001-15571 Rev. *E

Page 5 of 23

[+] Feedback