CXD2598Q Ver la hoja de datos (PDF) - Sony Semiconductor

Número de pieza

componentes Descripción

Fabricante

CXD2598Q Datasheet PDF : 147 Pages

| |||

CXD2598Q

Notes) • PCMD is a MSB first, two's complement output.

• GTOP is used to monitor the frame sync protection status. (High: sync protection window opens.)

• XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before

sync protection.

• XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the

EFM signal transition point coincide.

• The GFS signal goes high when the frame sync and the insertion protection timing match.

• RFCK is derived from the crystal accuracy, and has a cycle of 136µs.

• C2PO represents the data error status.

• XRAOF is generated when the 32K RAM exceeds the ±28F jitter margin.

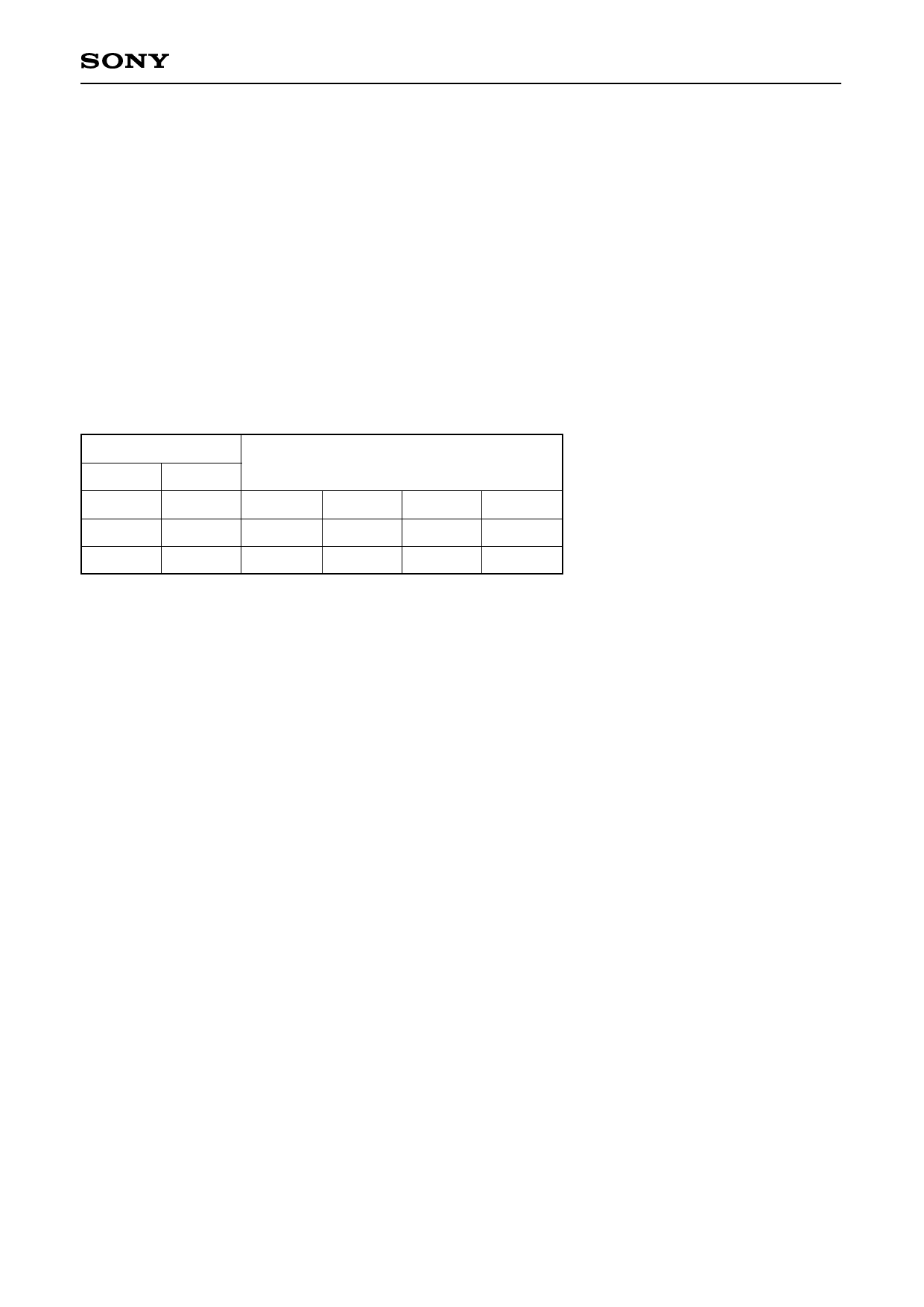

Monitor Pin Output Combinations

Command bit

MTSL1 MTSL0

0

0

0

1

1

0

XUGF

MNT0

RFCK

Output data

XPCK

MNT1

XPCK

GFS

MNT2

XROF

C2PO

MNT3

GTOP

–7–