CTM8B57EP Ver la hoja de datos (PDF) - CERAMATE TECHNICAL

Número de pieza

componentes Descripción

Fabricante

CTM8B57EP Datasheet PDF : 23 Pages

| |||

CTM8B54E/55E/56E/57E

EPROM-Based 8-Bit CMOS Microcontroller

Mnemonic

Operands

Description

Cycles

Instruction

Code

Status

Affected

DECR R, d Decrement R

1

01 0110 drrr rrrr Z

DECRSZ R, d Decrement R, Skip if 0

1 or

01 0111 drrr rrrr None

2(skip)

SUBAR R, d Subtract Acc from R

1

01 1010 drrr rrrr C, DC, Z

XORAR R, d Exclusive OR Acc with R

1

01 1011 drrr rrrr Z

ANDAR R, d AND Acc with R

1

01 0100 drrr rrrr Z

ADDAR R, d Add Acc and R

1

01 0101 drrr rrrr C, DC, Z

IORAR R, d Inclusive OR Acc with R

1

01 1111 drrr rrrr Z

Note:

b : Bit position

i : Immediate data

WDT : Watchdog Timer

Acc : Accumulator

R : Register address

T0MODE : T0MODE register

PD : Power down flag TO : Time overflow bit

IOST : I/O port status register

Z : Zero flag

C : Carry flag

DC : Digital carry flag

I : (i7i6i5i4i3i2i1i0)

d ∈ [0, 1] :Destination

R : (r6r5r4r3r2r1r0)

If d is “0”, the result is stored in the Acc register.

If d is “1”, the result is stored back in register R.

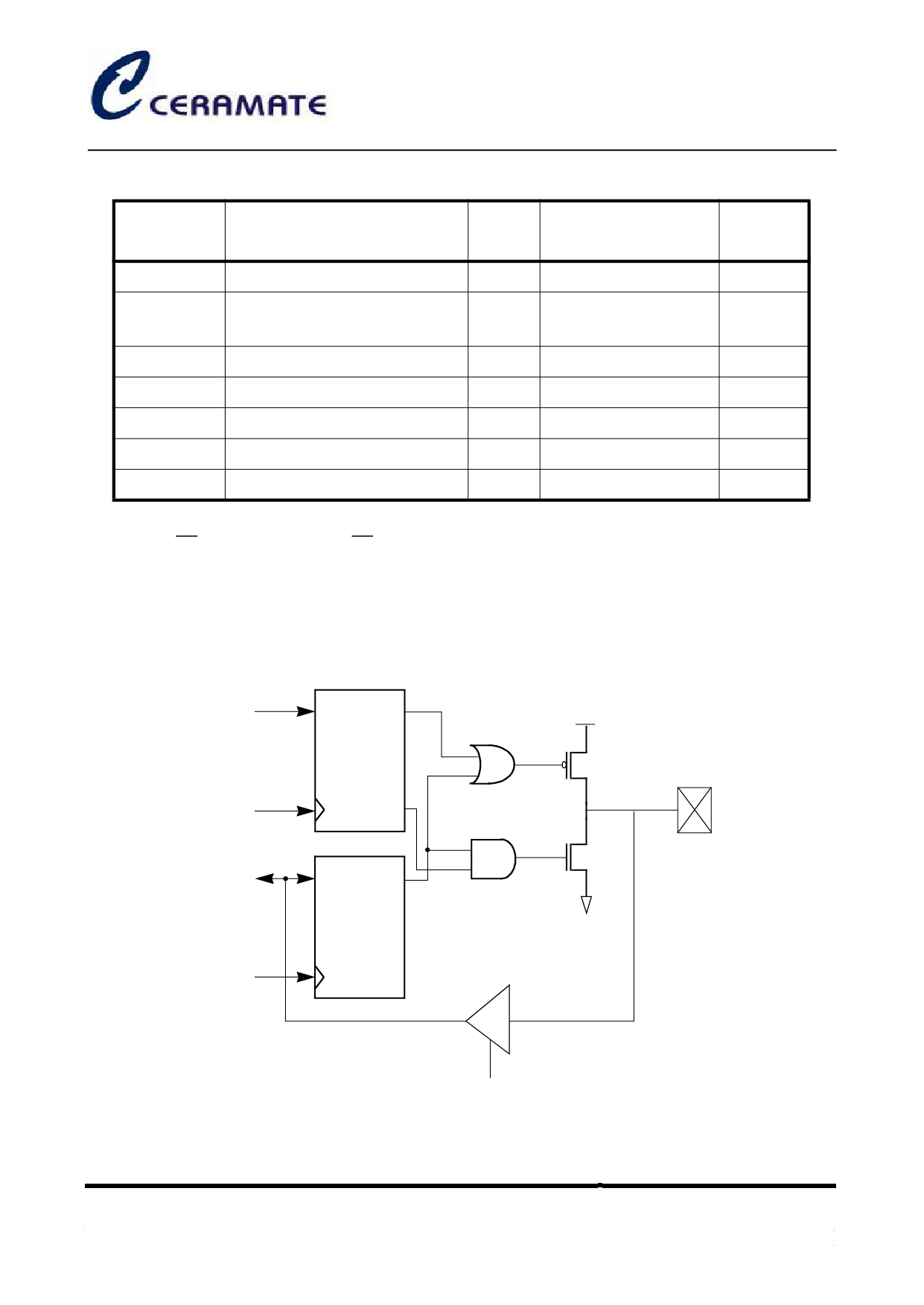

3.3 I/O PORTS EQUIVALENT CIRCUIT

Acc Data

D

Q

VDD

IOST

Latch

IOST R

CK

QB

I/O Pin

Data Bus

D

QB

Data

VSS

Latch

WR Port

CK

Q

RD Port

Note : 1. The IOST registers are “write-only” and set upon RESET.

2. If the IOST latch is “0”, the corresponding I/O pin is in output mode;

if the IOST latch is “1”, the corresponding I/O pin is in input mode.

* All specs and applications shown above subject to change without prior notice.

1F-5 NO.66 SEC.2 NAN-KAN RD ., LUCHU , TAOYUAN, TAIWAN, R.O.C

Tel:886-3-3529445

Fax:886 -3 -3521052

Page 8 of 23

Email: server@ceramate.com.tw

Http: www.ceramate.com.tw

Rev 1.1 Dec 26,2001