CTM8B55E Ver la hoja de datos (PDF) - CERAMATE TECHNICAL

Número de pieza

componentes Descripción

Fabricante

CTM8B55E Datasheet PDF : 23 Pages

| |||

CTM8B54E/55E/56E/57E

EPROM-Based 8-Bit CMOS Microcontroller

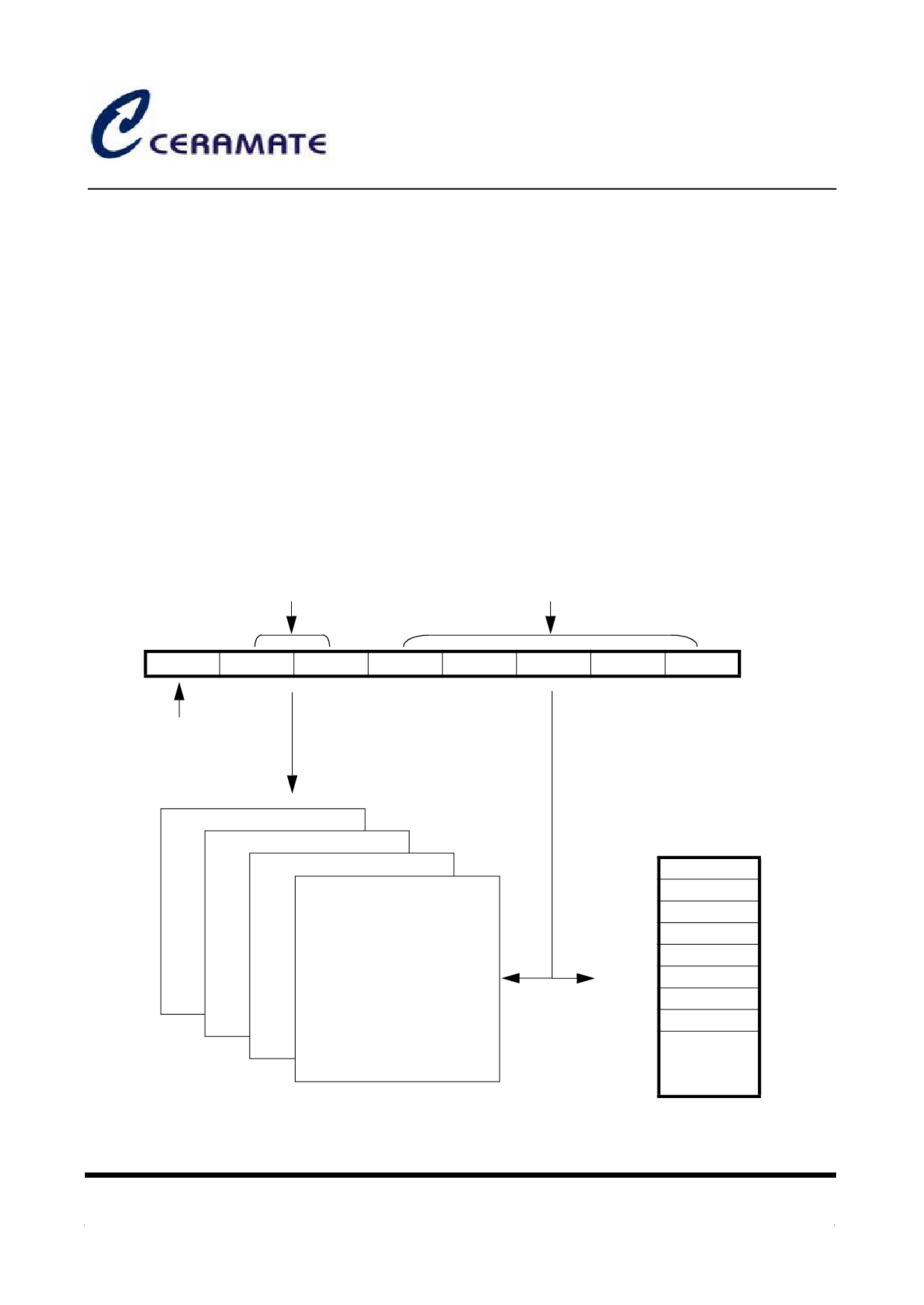

3.1.5 FSR(File select register pointer): R4

Bit 0~4 are used to select up to 32 registers (address: 00h~1Fh) and Bit 5~6 are Bank Select (Bank0~3) in the

indirect addressing mode shown in Figure 2.

3.1.6 PORT A: R5

PA3:PA0, bi-directional I/O Register

3.1.7 PORT B: R6

PB7:PB0, bi-directional I/O Register

3.1.8 PORT C: R7

PB7:PB0, bi-directional I/O Register, and for MTU8B55E/57E only

3.1.9 T0MODE REGISTER: T0MODE is a write-only register and the content is listed in Table 2.

3.1.10 IOST (Control Port I/O Mode Register)

The IOST register is “write-only”

= 0, I/O pin in output mode;

= 1, I/O pin in input mode.

Bank Select

Indirect Addressing Mode

Location Select

B7

B6

B5

B4

B3

B2

B1

B0

Read 1

70h

Bank 3

50h

Bank 2

30h

Bank 1

Bank 0

10h

7Fh

5Fh

3Fh

16 Bytes

SRAM

1Fh

FIGURE 2. Data Memory Configuraion

00h

INAR

01h

Timer0

02h

PC

03h STATUS

04h

FSR

05h PORT A

06h PORT B

07h PORT C

08h

8 Bytes

0Fh

SRAM

Bank 0

* All specs and applications shown above subject to change without prior notice.

1F-5 NO.66 SEC.2 NAN-KAN RD ., LUCHU , TAOYUAN, TAIWAN, R.O.C

Tel:886-3-3529445

Fax:886 -3 -3521052

Page 5 of 23

Email: server@ceramate.com.tw

Http: www.ceramate.com.tw

Rev 1.1 Dec 26,2001