VN16117L1 Ver la hoja de datos (PDF) - Vaishali Semiconductor

Número de pieza

componentes Descripción

Fabricante

VN16117L1 Datasheet PDF : 15 Pages

| |||

VN16117

Preliminary

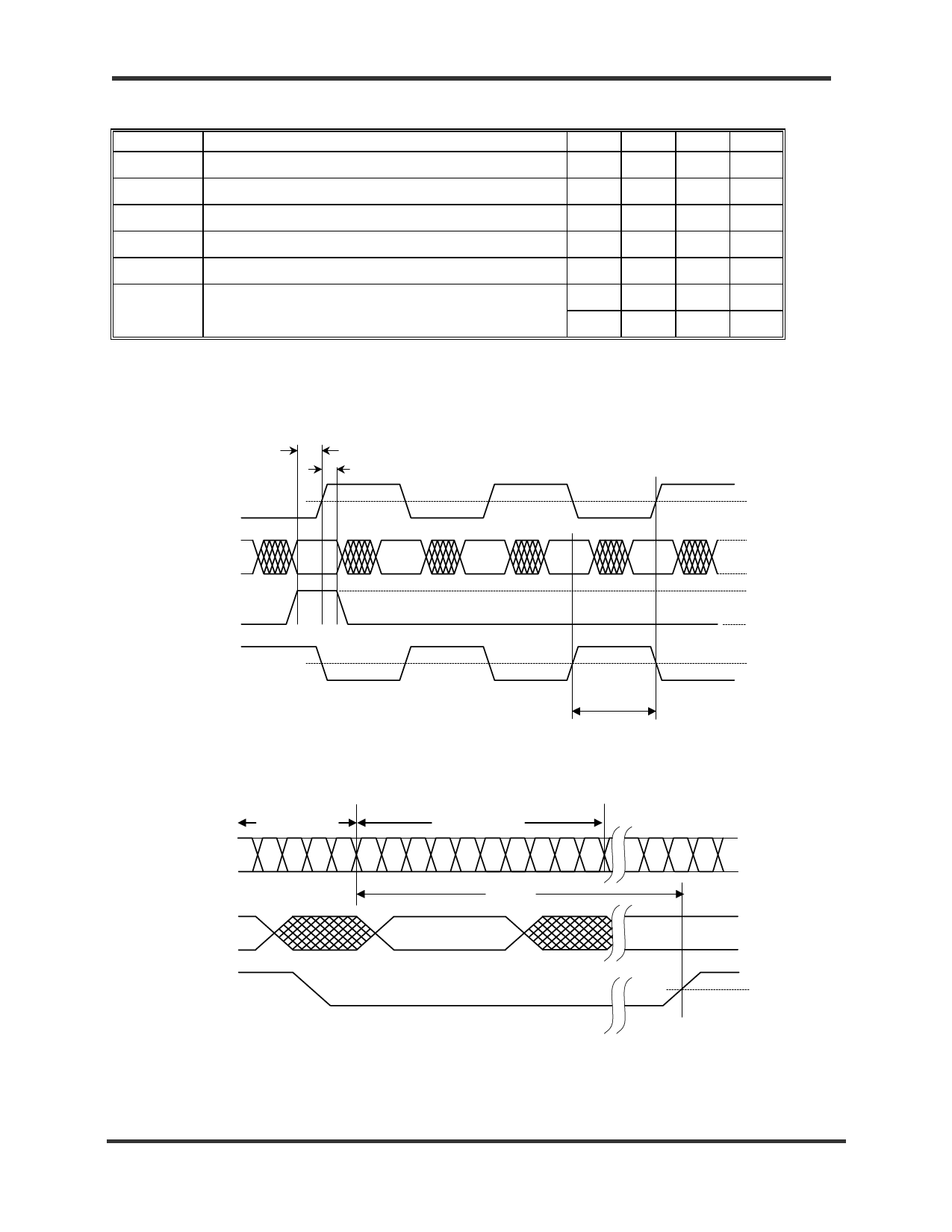

Table 8. Receiver Timing Characteristics

TA = 0°C to +70°C, VDD = 3.15 V to 3.45 V

Symbol

Parameter

b_sync[1]

Bit Sync Time

Min. Typ. Max. Unit

2500 bits

tSETUP

Data Setup Before Rising Edge of RX_CLK

3.0

nsec

tHOLD

Data Hold After Rising Edge of RX_CLK

1.5

nsec

tDUTY

RX_CLK Duty Cycle

40

60

%

tA-B

T_rxlat[2]

RX_CLK Skew

Receiver Latency

8.9 9.4 9.9 nsec

24.5

nsec

26.0

bits

Notes:

1. This is the recovery for input phase jumps.

2. The receiver latency as shown inFigure 6, is defined as the time between receiving the first serial bit of a parallel

data word (defined as the first edge of the first serial bit) and the clocking out of that parallel word (defined by

the rising edge of the receive byte clock, either RBC1 or RBC0).

tSETUP

RX_CLK<1>

tHOLD

1.4 V

RX<9:0>

COM_DET

K28.5

DATA

DATA

DATA

DATA

2.0 V

0.8 V

2.0 V

0.8 V

RX_CLK<0>

1.4 V

tA-B

Figure 5. Receiver Section Timing

DIN±

DATA BYTE C

DATA BYTE D

R5 R6 R7 R8 R9 R0 R1 R2 R3 R4 R5 R6 R7 R8 R9

RX<9:0>

t_rxlat

DATA BYTE A

R2 R3 R4 R5

DATA BYTE D

RX_CLK<1>/<0>

1.4 V

Figure 6. Receiver Latency

2001-08-09

Page 10

MDSN-0002-02

www.vaishali.com

Vaishali Semiconductor 747 Camden Avenue, Suite C Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063