ATTINY20-XUR Ver la hoja de datos (PDF) - Atmel Corporation

Número de pieza

componentes Descripción

Fabricante

ATTINY20-XUR Datasheet PDF : 219 Pages

| |||

4.8 Register Description

4.8.1 CCP – Configuration Change Protection Register

Bit

0x3C

Read/Write

Initial Value

7

6

5

4

3

2

1

0

CCP[7:0]

CCP

W

W

W

W

W

W

W

R/W

0

0

0

0

0

0

0

0

z Bits 7:0 – CCP[7:0]: Configuration Change Protection

In order to change the contents of a protected I/O register the CCP register must first be written with the correct

signature. After CCP is written the protected I/O registers may be written to during the next four CPU instruction cycles.

All interrupts are ignored during these cycles. After these cycles interrupts are automatically handled again by the CPU,

and any pending interrupts will be executed according to their priority.

When the protected I/O register signature is written, CCP0 will read as one as long as the protected feature is enabled,

while CCP[7:1] will always read as zero.

Table 4-1 shows the signatures that are recognized.

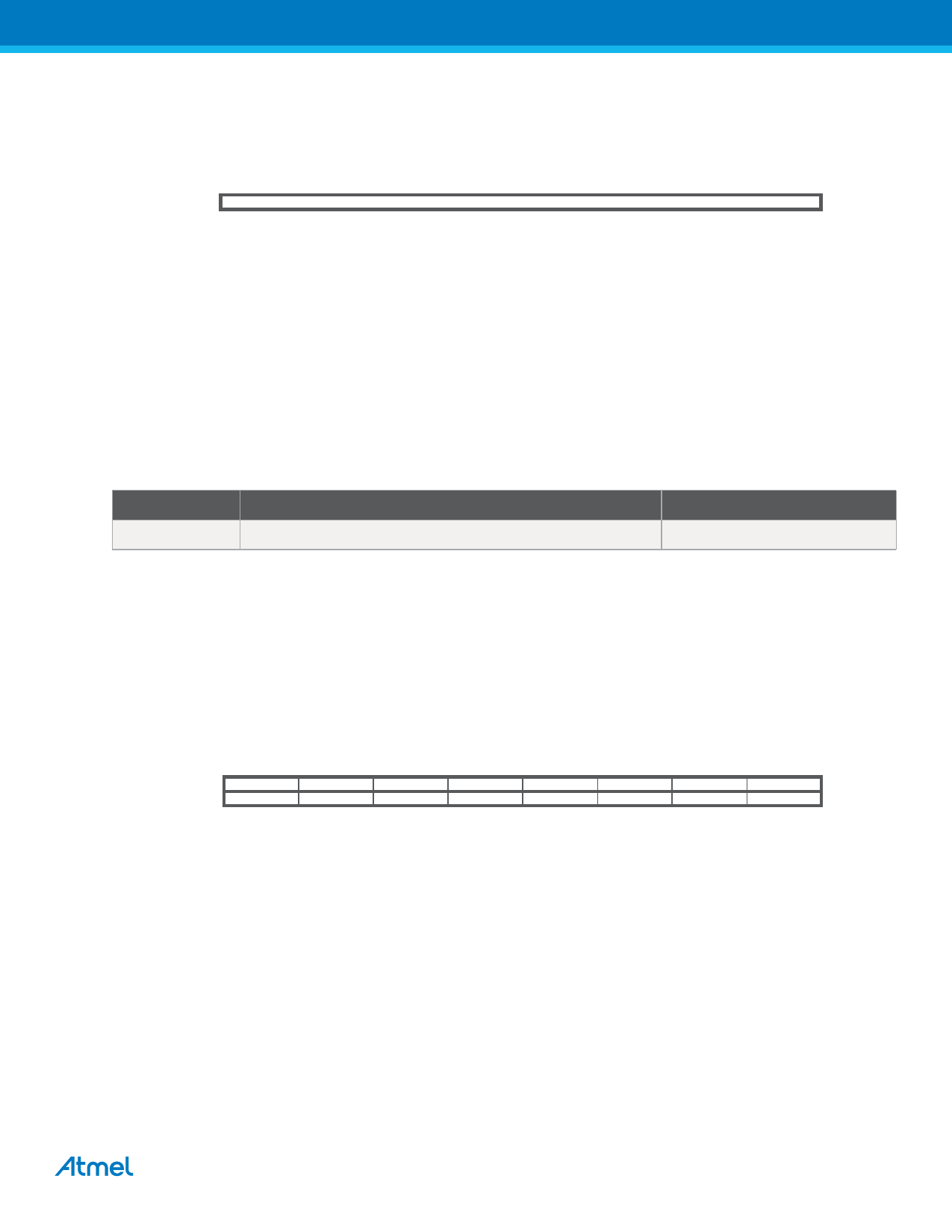

Table 4-1. Signatures Recognized by the Configuration Change Protection Register

Signature

0xD8

Group

IOREG: CLKMSR, CLKPSR, WDTCSR(1), MCUCR(2)

Description

Protected I/O register

Notes: 1. Only WDE and WDP[3:0] bits are protected in WDTCSR.

2. Only BODS bit is protected in MCUCR.

4.8.2 SPH and SPL — Stack Pointer Registers

Initial Value

Read/Write

Bit

0x3E

0x3D

Bit

Read/Write

Initial Value

0

R

15

–

SP7

7

R/W

RAMEND

0

R

14

–

SP6

6

R/W

RAMEND

0

R

13

–

SP5

5

R/W

RAMEND

0

R

12

–

SP4

4

R/W

RAMEND

0

R

11

–

SP3

3

R/W

RAMEND

0

R

10

–

SP2

2

R/W

RAMEND

0

R

9

–

SP1

1

R/W

RAMEND

0

R

8

–

SP0

0

R/W

RAMEND

SPH

SPL

z Bits 7:0 – SP[7:0]: Stack Pointer

The Stack Pointer register points to the top of the stack, which is implemented growing from higher memory locations to

lower memory locations. Hence, a stack PUSH command decreases the stack pointer.

The stack space in the data SRAM must be defined by the program before any subroutine calls are executed or

interrupts are enabled.

In ATtiny20, the SPH register has not been implemented.

ATtiny20 [DATASHEET] 13

Atmel-8235F-AVR-ATtiny20-Datasheet_09/2014