ATTINY12(2003) Ver la hoja de datos (PDF) - Atmel Corporation

Número de pieza

componentes Descripción

Fabricante

ATTINY12 Datasheet PDF : 91 Pages

| |||

General-purpose

Register File

1006D–AVR–07/03

ATtiny11/12

Figure 6. The ATtiny11/12 AVR RISC Architecture

8-bit Data Bus

512 x 16

Program

Flash

Program

Counter

Instruction

Register

Direct Addressing

Instruction

Decoder

Control Lines

Status

and Test

32 x 8

General-

purpose

Registers

ALU

64 x 8 EEPROM

(ATtiny12 only)

Control

Registers

Interrupt

Unit

SPI Unit

(ATtiny12 only)

8-bit

Timer/Counter

Watchdog

Timer

Analog

Comparator

6

I/O Lines

A flexible interrupt module has its control registers in the I/O space with an additional

global interrupt enable bit in the status register. All the different interrupts have a sepa-

rate interrupt vector in the interrupt vector table at the beginning of the

program memory. The different interrupts have priority in accordance with their interrupt

vector position. The lower the interrupt vector address, the higher the priority.

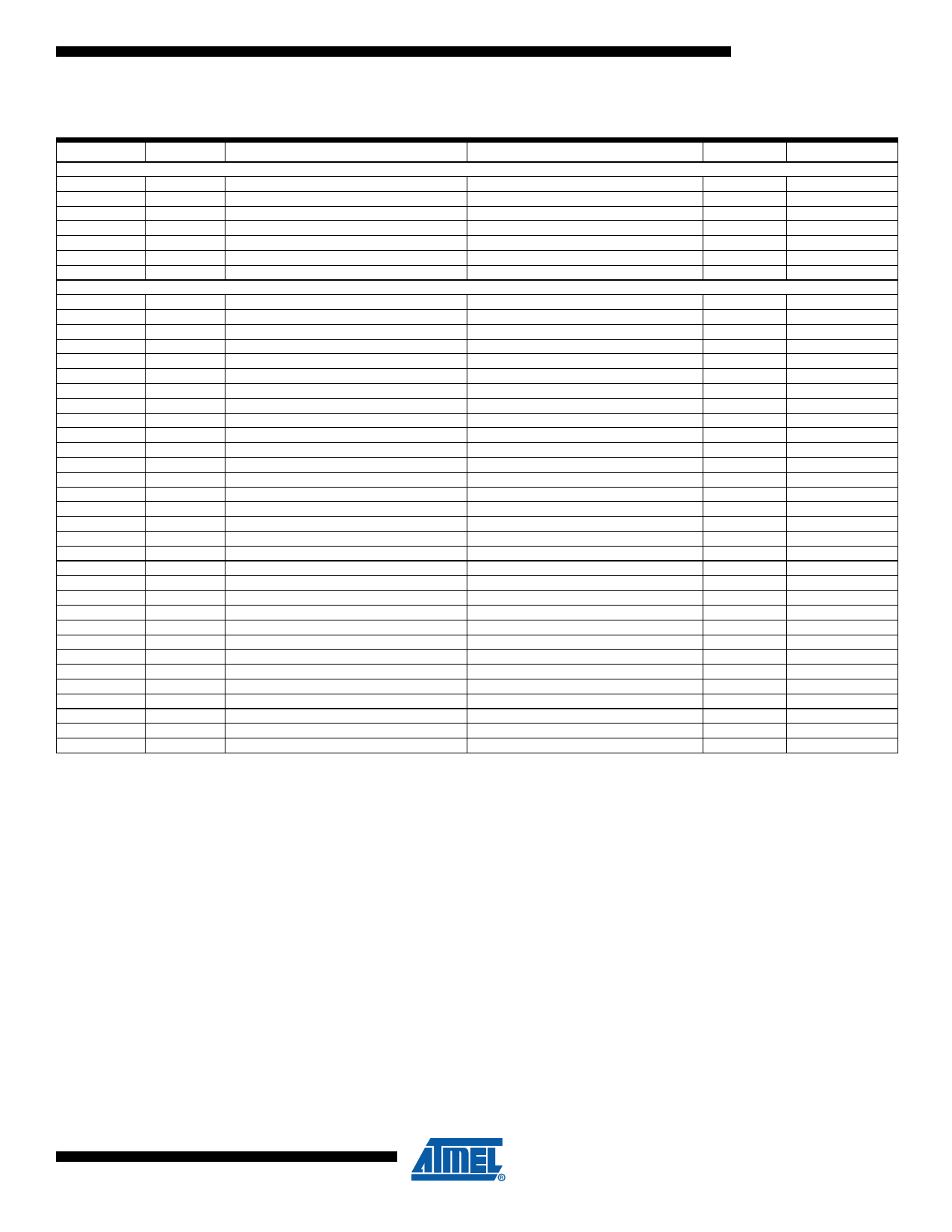

Figure 7 shows the structure of the 32 general-purpose registers in the CPU.

Figure 7. AVR CPU General-purpose Working Registers

General-

purpose

Working

Registers

7

0

R0

R1

R2

…

…

R28

R29

R30 (Z-register low byte)

R31 (Z-register high byte)

All the register operating instructions in the instruction set have direct- and single-cycle

access to all registers. The only exception is the five constant arithmetic and logic

instructions SBCI, SUBI, CPI, ANDI, and ORI between a constant and a register and the

LDI instruction for load-immediate constant data. These instructions apply to the second

half of the registers in the register file – R16..R31. The general SBC, SUB, CP, AND,

9