AS1161 Ver la hoja de datos (PDF) - austriamicrosystems AG

Número de pieza

componentes Descripción

Fabricante

AS1161

AS1161 Datasheet PDF : 29 Pages

| |||

AS1160/AS1161

Datasheet - Electrical Characteristics

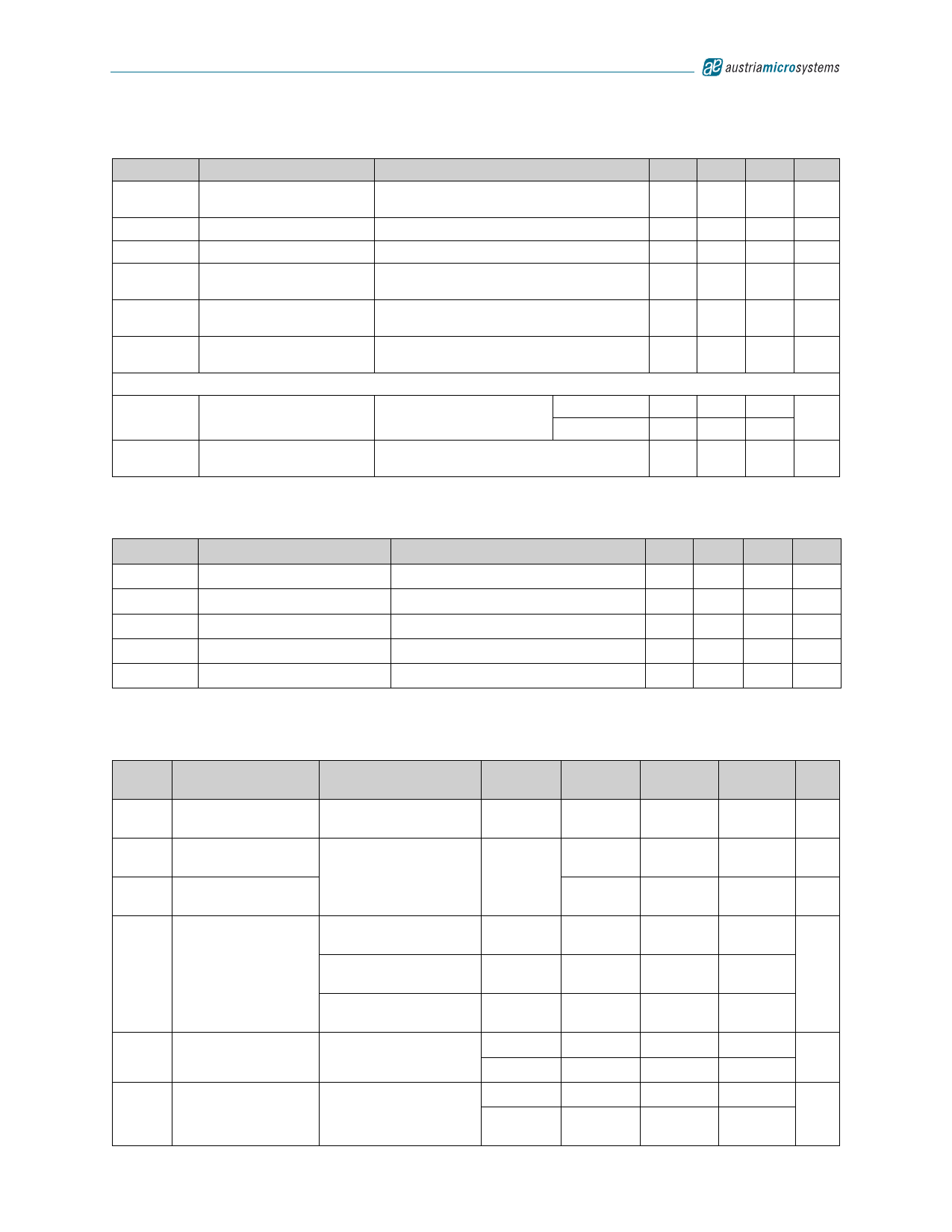

Table 7. Electrical Characteristics (Continued)

Symbol

Parameter

Conditions

IILR

Input Current, TMS, TDI,

TRSTN inputs

VIN = 0V

VOH

High Level Output Voltage

IOH = -4 mA

VOL

Low Level Output Voltage

IOH = 4 mA

IOS

Output Short Circuit

Current

VOUT = 0V

IOS

Output Short Circuit

Current, TDO output

IOZ

Tri-State Output Current

PWDNN or REN = 0V,

VOUT = 0V or VDD

Deserializer Supply Current (pins DVDD and AVDD)

ICCR

Deserializer Supply

Current (Worst Case)

Figure 17 on page 12

f = 20MHz

f = 66MHz

ICCXR

Deserializer Supply

Current (Powerdown)

PWDNN = 0V, REN = 0V

Min Typ Max Unit

-30 -60 µA

2.2 3.0 VDD V

GND 0.25 0.5 V

-15 -35 -60 mA

-80 -150 -220 mA

-1

+1 µA

45 60

mA

100 130

0.75 1.0 mA

Deserializer Timing Requirements for REFCLK

Table 8. Deserializer Timing Requirements for REFCLK

Symbol

Parameter

fRFCLK

REFCLK Frequency

tRFCP

REFCLK Period

tRFDC

REFCLK Duty Cycle

tRFCP/tTCP

REFCLK-to-TCLK Ratio

tRFTT

REFCLK Transition Time

Conditions

Min Typ Max Unit

20

66 MHz

15.15 T

50 ns

30 50 70 %

95

1 105

3

6

ns

Deserializer Switching Characteristics

Table 9. Deserializer Switching Characteristics1

Symbol

Parameter

Conditions

Pin/

Frequency

Min

Typ

Max Unit

tRCP

Receiver Out Clock

Period

tRCP = tTCP,

Figure 26 on page 15

RCLK

15.15

50

ns

tCLH

CMOS/TTL Low-to-

High Transition Time

Figure 19 on page 13

tCHL

CMOS/TTL High-to-

Low Transition Time

RCLK,

ROUTx,

LOCKN

1.5

4

ns

1.4

4

ns

All temperatures, all

frequencies

1.6 x tRCP

+ 1.0

1.75 x tRCP

+ 7.0

tDD

Deserializer Delay,

Figure 27 on page 16

Room temperature, 3.3V

20MHz

1.6 x tRCP 1.6 x tRCP 1.6 x tRCP

+ 2.0

+ 4.0

+ 6.0

ns

Room temperature, 3.3V

66MHz

1.75 x tRCP 1.75 x tRCP 1.75 x tRCP

+ 2.0

+ 4.0

+ 6.0

tROS

ROUT Data Valid

Before RCLK Time

Figure 28 on page 16

20MHz

66MHz

0.4 x tRCP 0.5 x tRCP

0.38 x tRCP 0.5 x tRCP

ns

20MHz -0.4 x tRCP 0.5 x tRCP

tROH

ROUT Data Valid After

RCLK Time

Figure 28 on page 16

66MHz

-0.38 x

tRCP

-0.5 x tRCP

ns

www.austriamicrosystems.com/Interfaces-LVDS/AS1160_61

Revision 1.01

8 - 29