AN8018SA Ver la hoja de datos (PDF) - Panasonic Corporation

Número de pieza

componentes Descripción

Fabricante

AN8018SA

AN8018SA Datasheet PDF : 26 Pages

| |||

AN8018SA

Voltage Regulators

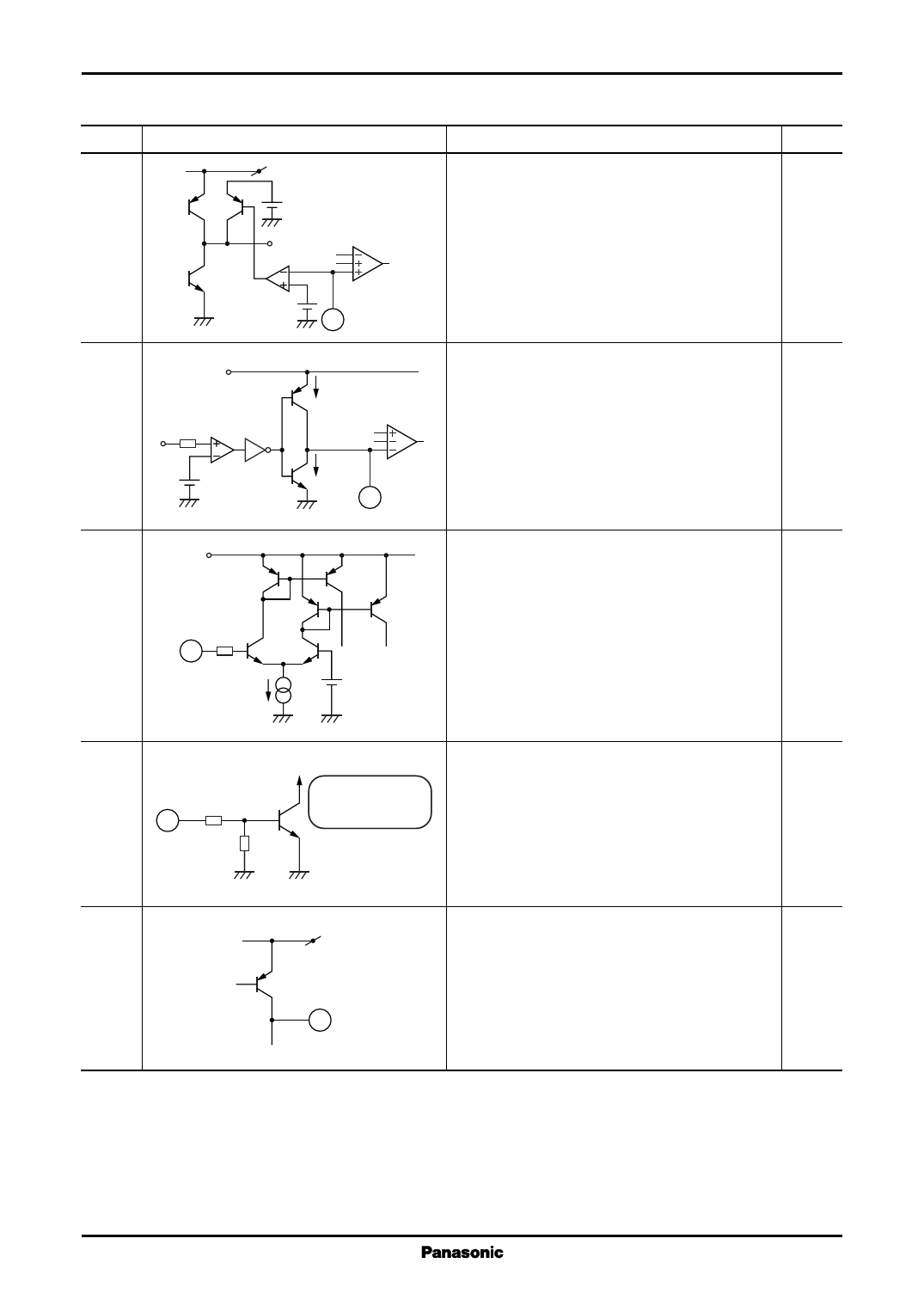

s Terminal Equivalent Circuits (continued)

Pin No.

Equivalent circuit

12

VCC

0.9 V

FB2 OSC PWM

0.9 V

12

Description

I/O

DT2:

I

The pin for setting channel 2 output maximum

duty ratio.

If this terminal is set at a voltage of 0.9 V or more,

FB2 terminal becomes high-level voltage and the

protective function for channel 2 output short-

circuit will stop (Unlatch function).

13

VCC

IN+2

1.19 V

FB2:

O

47 µA

The output pin for error amplifier 2 block.

The source current is −47 µA and the sink current

OSC PWM is 47 µA.

47 µA

Correct the frequency characteristics of the gain

and the phase by connecting a resistor and a ca-

13

pacitor between this terminal and GND.

14

VCC

IN+2:

I

The noninverting input pin for error amplifier 2

block.

14

100 Ω

1.19 V

15

30 kΩ

15

60 kΩ

16

Internal circuit

start/stop

VCC

16

Off:

I

The terminal for on/off control.

High-level input: Normal operation (VOFF > 1.3

V)

Low-level input: Standby state (VOFF < 0.8 V)

The total current consumption in the standby state

can be suppressed to a value 1 mA or less.

VREF:

O

The output terminal for the internal reference

voltage.

The reference voltage is 1.19 V (allowance: ± 2%) at

VCC = 2.4 V and IREF = − 0.1 mA.

Connect a capacitor of 0.01 µF or more between

VREF and GND for phase compensation.

8