AL700 Ver la hoja de datos (PDF) - AverLogic Technologies Inc

Número de pieza

componentes Descripción

Fabricante

AL700 Datasheet PDF : 82 Pages

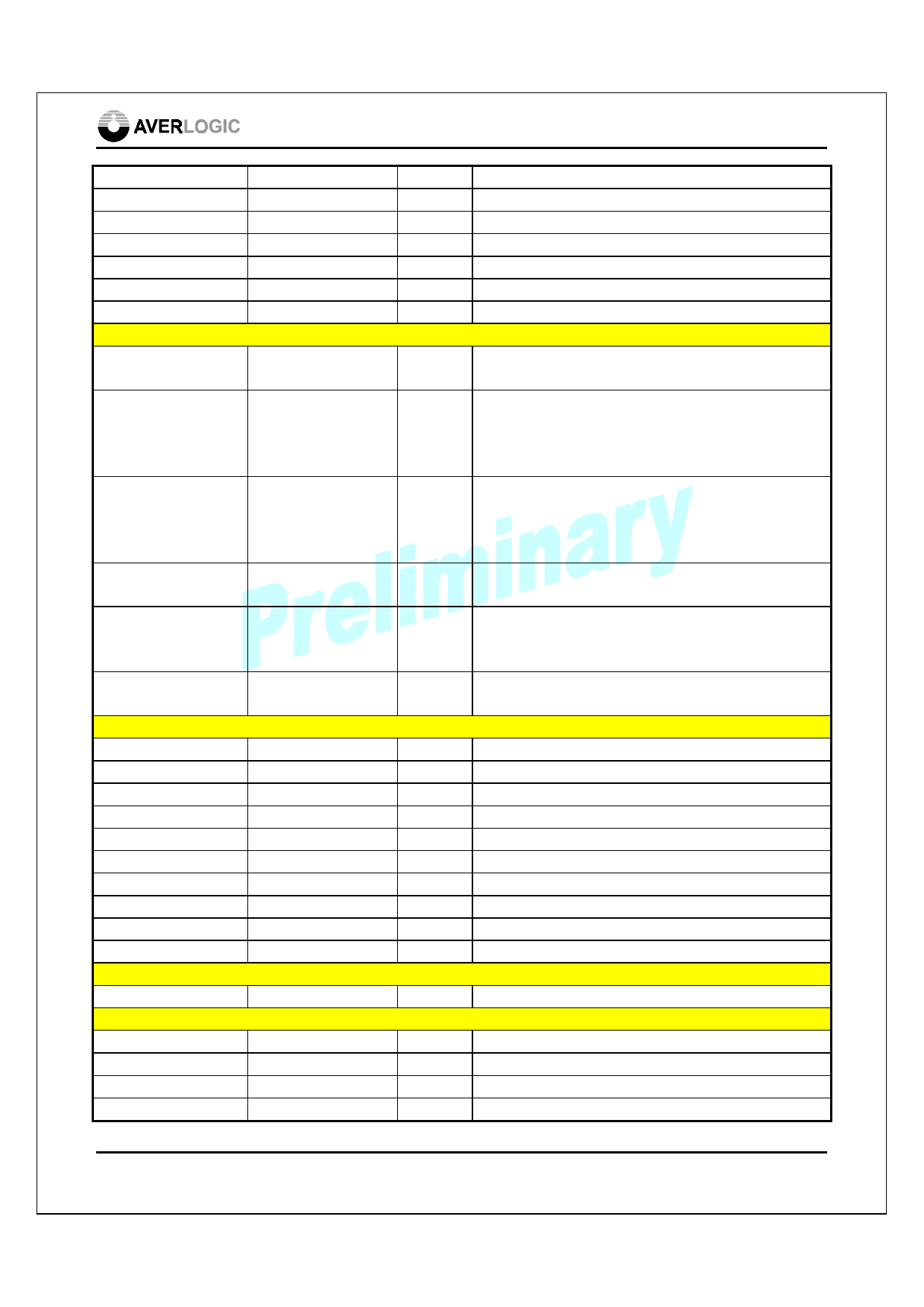

| |||

Pin Name

MD[15:0]

DQMH

DQML

CKE

DMCLK_I

DMCLK_O

Host Interface

SP_SEL

H_WRB

H_DENB

H_RDB

H_BUS[7:0]

INTR

Clock

XTI

XTO

XTI_NTSC

XTO_NTSC

XTI_PAL

XTO_PAL

PLL_AVDD

PLL_AVSS

PLL_VDD

PLL_VSS

System

RSTB

Others

TEST

TEST_DAC

H_RDYB

NC

AL700/701/710

Pin Number

16-23, 14-9, 7, 6

24

25

30

28

27

I/O type

Description

I/O Data bus for SDRAM

O High byte data mask for SDRAM

O Low byte data mask for SDRAM

O Clock enable for SDRAM

I Clock input for SDRAM controller

O Clock output for SDRAM

205

199

201

200

190-197

204

I Serial/parallel host interface selection, High for

serial mode and Low for parallel mode

I 1. Host write signal for parallel mode, active

Low to High trigger

2. Equivalent to SCL (serial clock) for I2C serial

mode

I 1. Host data enable signal for parallel mode,

Low for address and High for data

2. Slave address selection for I2C serial mode,

Low for 70h/71h and High for 72h/73h

I Host read enable signal, Low for read operation

and High for write operation

I/O Host stream data or address bus in parallel

mode. H_BUS7 is I2C data line (SDA) in serial

mode

O Interrupt output for motion detection, video loss

or other events

182

I 27MHz OSC input

183

O 27MHz OSC output

207

I 28.6364MHz OSC input

208

O 28.6364MHz OSC output

3

I 35.4690MHz OSC input

4

O 35.4690MHz OSC output

187

AP Analog power for PLL

185

AP Analog ground for PLL

188

DP Digital power for PLL

184

DP Digital ground for PLL

189

I System reset, active Low

103

52

202

1, 186

I Factory test pin

I Factory test pin

O Reserved

- No connection

©2001,2002-Copyright by AverLogic Technologies, Corp. Preliminary Version C1.1 11