ADSP-BF514KSWZ-4 Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-BF514KSWZ-4 Datasheet PDF : 68 Pages

| |||

ADSP-BF512/BF512F, BF514/BF514F, BF516/BF516F, BF518/BF518F

GENERAL DESCRIPTION

The ADSP-BF512/ADSP-BF512F, ADSP-BF514/ADSP-

BF514F, ADSP-BF516/ADSP-BF516F, ADSP-BF518/ADSP-

BF518F processors are members of the Blackfin® family of prod-

ucts, incorporating the Analog Devices/Intel Micro Signal

Architecture (MSA). Blackfin processors combine a dual-MAC

state-of-the-art signal processing engine, the advantages of a

clean, orthogonal RISC-like microprocessor instruction set, and

single-instruction, multiple-data (SIMD) multimedia capabili-

ties into a single instruction-set architecture.

The processors are completely code compatible with other

Blackfin processors.

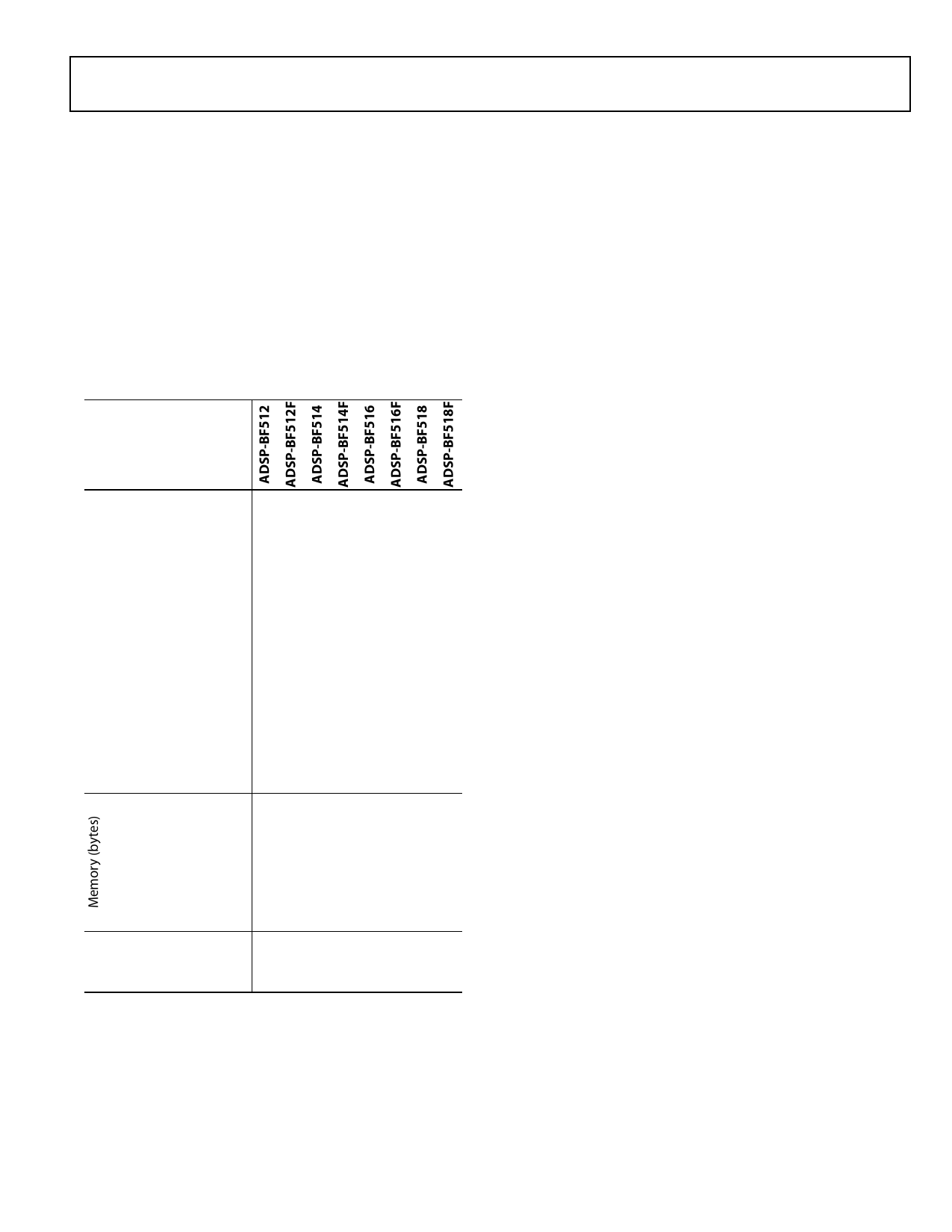

Table 1. Processor Comparison

Feature

IEEE-1588

Ethernet MAC

RSI

TWI

SPORTs

UARTs

SPIs

GP Timers

Watchdog Timers

RTC

PPI

Internal 4 Mbit SPI flash

Rotary Counter

3-Phase PWM Pairs

GPIOs

L1 Instruction SRAM

L1 Instruction

SRAM/Cache

L1 Data SRAM

L1 Data SRAM/Cache

L1 Scratchpad

L3 Boot ROM

Maximum Speed Grade

Package Options

––––––11

––––1111

––111111

11111111

22222222

22222222

22222222

88888888

11111111

11111111

11111111

–1–1–1–1

11111111

33333333

40 40 40 40 40 40 40 40

32K

16K

32K

32K

4K

32K

400 MHz

176-Lead LQFP with Exposed Pad

168-Ball CSP_BGA

By integrating a rich set of industry-leading system peripherals

and memory, Blackfin processors are the platform of choice for

next-generation applications that require RISC-like program-

mability, multimedia support, and leading-edge signal

processing in one integrated package.

PORTABLE LOW POWER ARCHITECTURE

Blackfin processors provide world-class power management

and performance. They are produced with a low power and low

voltage design methodology and feature on-chip dynamic

power management, which is the ability to vary both the voltage

and frequency of operation to significantly lower overall power

consumption. This capability can result in a substantial reduc-

tion in power consumption, compared with just varying the

frequency of operation. This allows longer battery life for

portable appliances.

SYSTEM INTEGRATION

The ADSP-BF51x processors are highly integrated system-on-a-

chip solutions for the next generation of embedded network

connected applications. By combining industry-standard inter-

faces with a high performance signal processing core, cost-

effective applications can be developed quickly, without the

need for costly external components. The system peripherals

include an IEEE-compliant 802.3 10/100 Ethernet MAC with

IEEE-1588 support (ADSP-BF518/ADSP-BF518F only), an RSI

controller, a TWI controller, two UART ports, two SPI ports,

two serial ports (SPORTs), nine general-purpose 32-bit timers

(eight with PWM capability), 3-phase PWM for motor control,

a real-time clock, a watchdog timer, and a parallel peripheral

interface (PPI).

BLACKFIN PROCESSOR CORE

As shown in Figure 1, the Blackfin processor core contains two

16-bit multipliers, two 40-bit accumulators, two 40-bit ALUs,

four video ALUs, and a 40-bit shifter. The computation units

process 8-, 16-, or 32-bit data from the register file.

The compute register file contains eight 32-bit registers. When

performing compute operations on 16-bit operand data, the

register file operates as 16 independent 16-bit registers. All

operands for compute operations come from the multiported

register file and instruction constant fields.

Each MAC can perform a 16-bit by 16-bit multiply in each

cycle, accumulating the results into the 40-bit accumulators.

Signed and unsigned formats, rounding, and saturation

are supported.

The ALUs perform a traditional set of arithmetic and logical

operations on 16-bit or 32-bit data. In addition, many special

instructions are included to accelerate various signal processing

tasks. These include bit operations such as field extract and pop-

ulation count, modulo 232 multiply, divide primitives, saturation

and rounding, and sign/exponent detection. The set of video

instructions include byte alignment and packing operations,

16-bit and 8-bit adds with clipping, 8-bit average operations,

and 8-bit subtract/absolute value/accumulate (SAA) operations.

The compare/select and vector search instructions are also

provided.

Rev. B | Page 3 of 68 | January 2011