ADSP-BF514KSWZ-4 Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-BF514KSWZ-4 Datasheet PDF : 68 Pages

| |||

ADSP-BF512/BF512F, BF514/BF514F, BF516/BF516F, BF518/BF518F

Parallel Peripheral Interface (PPI)

The ADSP-BF51x processors provide a parallel peripheral inter-

face (PPI) that can connect directly to parallel analog-to-digital

and digital-to-analog converters, ITU-R-601/656 video encod-

ers and decoders, and other general-purpose peripherals. The

PPI consists of a dedicated input clock signal, up to three frame

synchronization signals, and up to 16 data signals.

In ITU-R-656 modes, the PPI receives and parses a data stream

of 8-bit or 10-bit data elements. On-chip decode of embedded

preamble control and synchronization information

is supported.

Three distinct ITU-R-656 modes are supported:

• Active video only mode—The PPI does not read in any

data between the End of Active Video (EAV) and Start of

Active Video (SAV) preamble symbols, or any data present

during the vertical blanking intervals. In this mode, the

control byte sequences are not stored to memory; they are

filtered by the PPI.

• Vertical blanking only mode—The PPI only transfers verti-

cal blanking interval (VBI) data, as well as horizontal

blanking information and control byte sequences on

VBI lines.

• Entire field mode—The entire incoming bitstream is read

in through the PPI. This includes active video, control pre-

amble sequences, and ancillary data that may be embedded

in horizontal and vertical blanking intervals.

Though not explicitly supported, ITU-R-656 output functional-

ity can be achieved by setting up the entire frame structure

(including active video, blanking, and control information) in

memory and streaming the data out the PPI in a frame sync-less

mode. The processor’s 2-D DMA features facilitate this transfer

by allowing the static frame buffer (blanking and control codes)

to be placed in memory once, and simply updating the active

video information on a per-frame basis.

The general-purpose modes of the PPI are intended to suit a

wide variety of data capture and transmission applications. The

modes are divided into four main categories, each allowing up

to 16 bits of data transfer per PPI_CLK cycle:

• Data receive with internally generated frame syncs

• Data receive with externally generated frame syncs

• Data transmit with internally generated frame syncs

• Data transmit with externally generated frame syncs

These modes support ADC/DAC connections, as well as video

communication with hardware signalling. Many of the modes

support more than one level of frame synchronization. If

desired, a programmable delay can be inserted between asser-

tion of a frame sync and reception/transmission of data.

Code Security with Lockbox Secure Technology

A security system consisting of a blend of hardware and soft-

ware provides customers with a flexible and rich set of code

security features with Lockbox® secure technology. Key features

include:

• OTP memory

• Unique chip ID

• Code authentication

• Secure mode of operation

The security scheme is based upon the concept of authentica-

tion of digital signatures using standards-based algorithms and

provides a secure processing environment in which to execute

code and protect assets.

DYNAMIC POWER MANAGEMENT

The ADSP-BF51x processors provide four operating modes,

each with a different performance/power profile. In addition,

dynamic power management provides the control functions to

dynamically alter the processor core supply voltage, further

reducing power dissipation. When configured for a 0 V core

supply voltage, the processor enters the hibernate state. Control

of clocking to each of the processor peripherals also reduces

power consumption. See Table 2 for a summary of the power

settings for each mode.

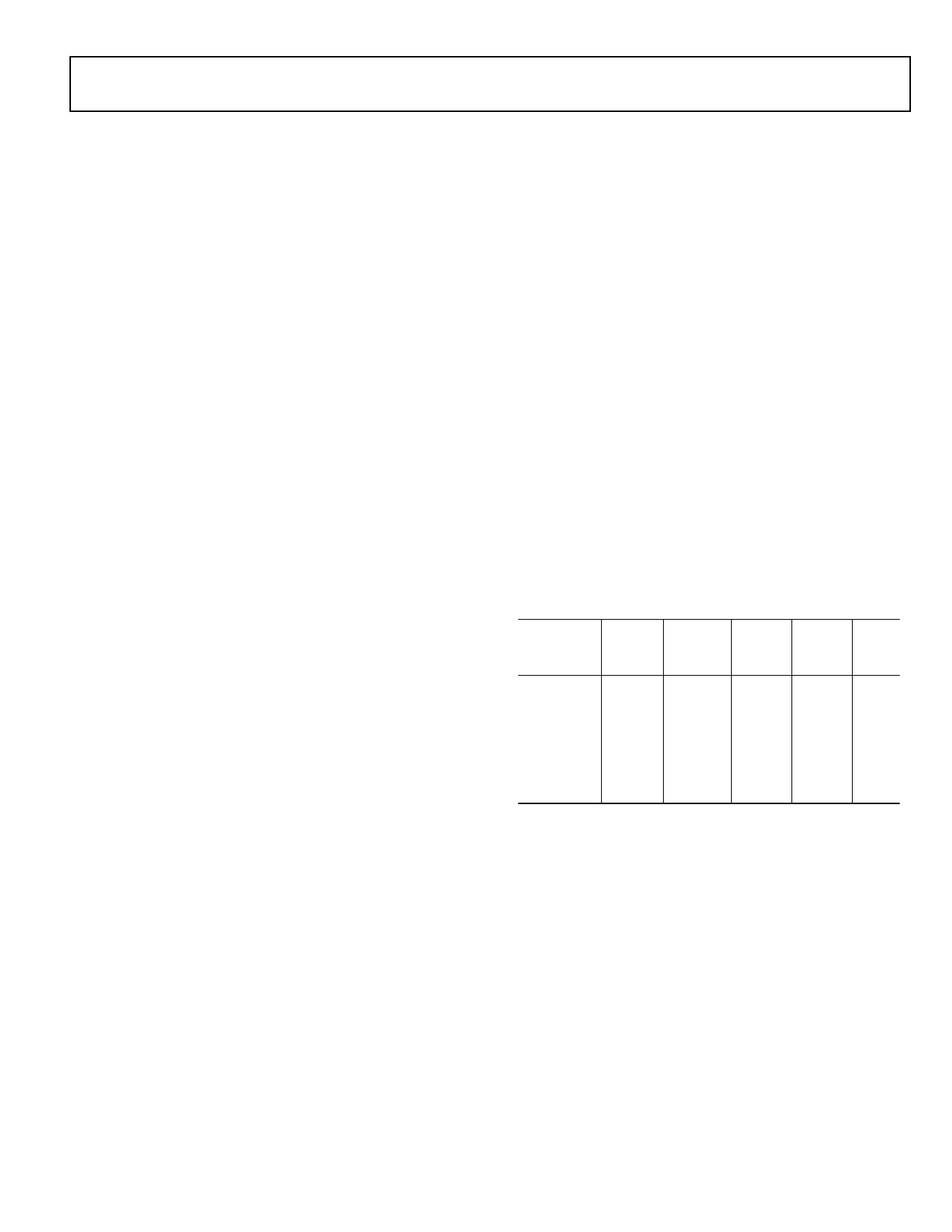

Table 2. Power Settings

Mode/State PLL

Core

PLL

Clock

Bypassed (CCLK)

System

Clock Core

(SCLK) Power

Full On

Enabled No

Enabled Enabled On

Active

Enabled/ Yes

Disabled

Enabled Enabled On

Sleep

Enabled —

Disabled Enabled On

Deep Sleep Disabled —

Disabled Disabled On

Hibernate Disabled —

Disabled Disabled Off

Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed,

providing capability for maximum operational frequency. This

is the power-up default execution state in which maximum per-

formance can be achieved. The processor core and all enabled

peripherals run at full speed.

Active Operating Mode—Moderate Power Savings

In the active mode, the PLL is enabled but bypassed. Because the

PLL is bypassed, the processor’s core clock (CCLK) and system

clock (SCLK) run at the input clock (CLKIN) frequency. In this

mode, the CLKIN to CCLK multiplier ratio can be changed,

although the changes are not realized until the full-on mode is

entered. DMA access is available to appropriately configured

L1 memories.

Rev. B | Page 11 of 68 | January 2011