ADSP-2196MKCA-160X Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-2196MKCA-160X Datasheet PDF : 68 Pages

| |||

35(/,0,1$5< 7(&+1,&$/ '$7$

September 2001 For current information contact Analog Devices at 800/262-5643

ADSP-2196

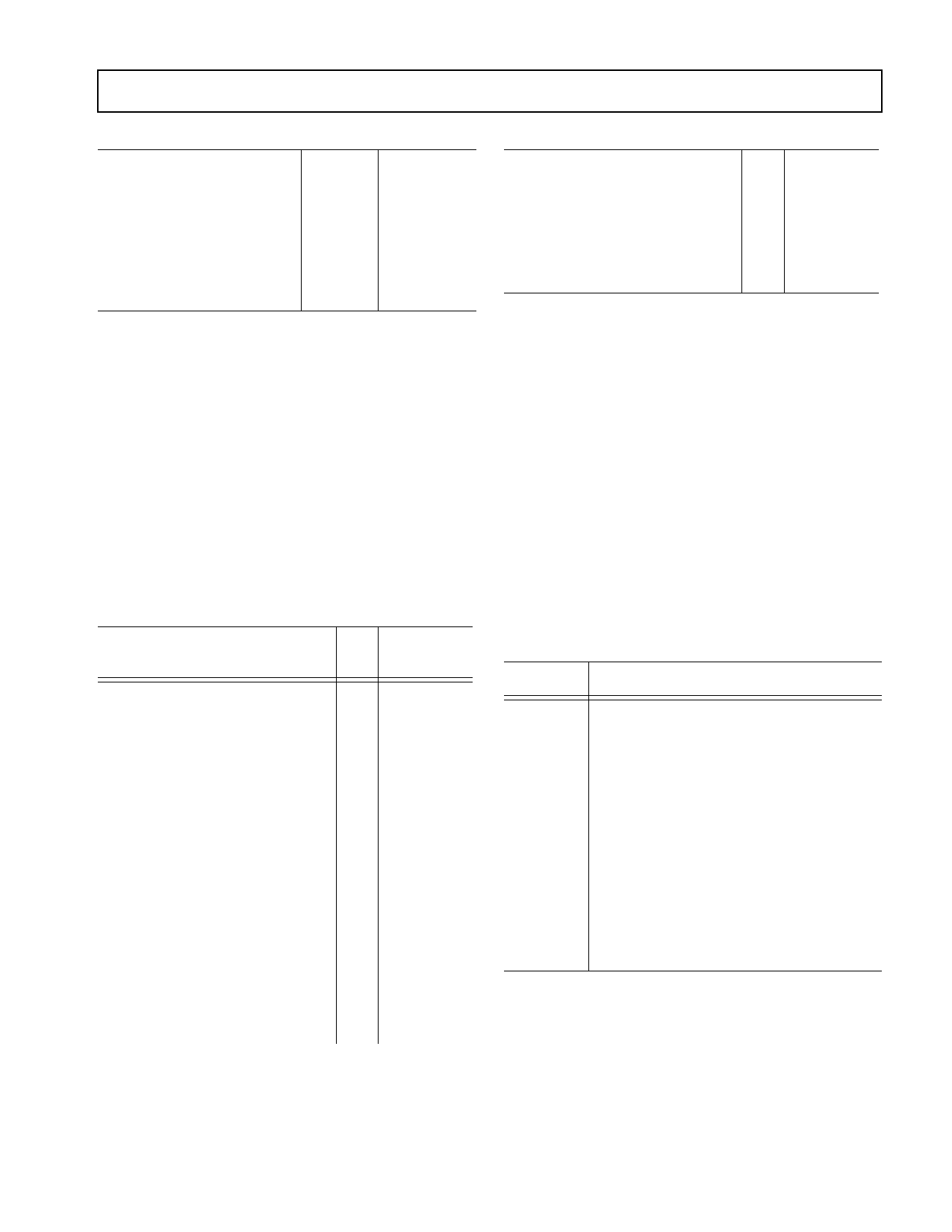

Table 1. Interrupt Priorities/Addresses (Continued)

Table 2. Peripheral Interrupts and Priority at Reset

Interrupt

IMASK/ Vector

IRPTL Address1

User Assigned Interrupt

13

0x00 01A0

User Assigned Interrupt

14

0x00 01C0

User Assigned Interrupt— 15

Lowest Priority

0x00 01E0

1These interrupt vectors start at address 0x10000 when the DSP is in

“no-boot”, run-form-external memory mode.

Table 2 shows the ID and priority at reset of each of the

peripheral interrupts. To assign the peripheral interrupts a

different priority, applications write the new priority to their

corresponding control bits (determined by their ID) in the

Interrupt Priority Control register. The peripheral inter-

rupt’s position in the IMASK and IRPTL register and its

vector address depend on its priority level, as shown in

Table 1. Because the IMASK and IRPTL registers are

limited to 16 bits, any peripheral interrupts assigned a

priority level of 11 are aliased to the lowest priority bit

position (15) in these registers and share vector address

0x00 01E0.

Table 2. Peripheral Interrupts and Priority at Reset

Interrupt

Slave DMA/Host Port Interface

SPORT0 Receive

SPORT0 Transmit

SPORT1 Receive

SPORT1 Transmit

SPORT2 Receive/SPI0

SPORT2 Transmit/SPI1

UART Receive

UART Transmit

Timer A

Timer B

Timer C

Reset

ID Priority

00

11

22

33

44

55

66

77

88

99

10 10

11 11

Interrupt

Programmable Flag 0 (any PFx)

Programmable Flag 1 (any PFx)

Memory DMA port

Reset

ID Priority

12 11

13 11

14 11

Interrupt routines can either be nested with higher priority

interrupts taking precedence or processed sequentially.

Interrupts can be masked or unmasked with the IMASK

register. Individual interrupt requests are logically ANDed

with the bits in IMASK; the highest priority unmasked

interrupt is then selected. The emulation, power-down, and

reset interrupts are nonmaskable with the IMASK register,

but software can use the DIS INT instruction to mask the

power-down interrupt.

The Interrupt Control (ICNTL) register controls interrupt

nesting and enables or disables interrupts globally. The gen-

eral-purpose Programmable Flag (PFx) pins can be

configured as outputs, can implement software interrupts,

and (as inputs) can implement hardware interrupts. Pro-

grammable Flag pin interrupts can be configured for

level-sensitive, single edge-sensitive, or dual edge-

sensitive operation.

Table 3. Interrupt Control (ICNTL) Register Bits

Bit

0–3

4

5

6

7

8–9

10

11

12–15

Description

Reserved

Interrupt Nesting Enable

Global Interrupt Enable

Reserved

MAC-Biased Rounding Enable

Reserved

PC Stack Interrupt Enable

Loop Stack Interrupt Enable

Reserved

The IRPTL register is used to force and clear interrupts.

On-chip stacks preserve the processor status and are auto-

matically maintained during interrupt handling. To support

interrupt, loop, and subroutine nesting, the PC stack is

33 levels deep, the loop stack is eight levels deep, and the

status stack is 16 levels deep. To prevent stack overflow, the

REV. PrA

This information applies to a product under development. Its characteristics and specifications are subject to change with-

9

out notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.