ADSP-21161NKCA-100(RevA) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

ADSP-21161NKCA-100 Datasheet PDF : 60 Pages

| |||

ADSP-21161N

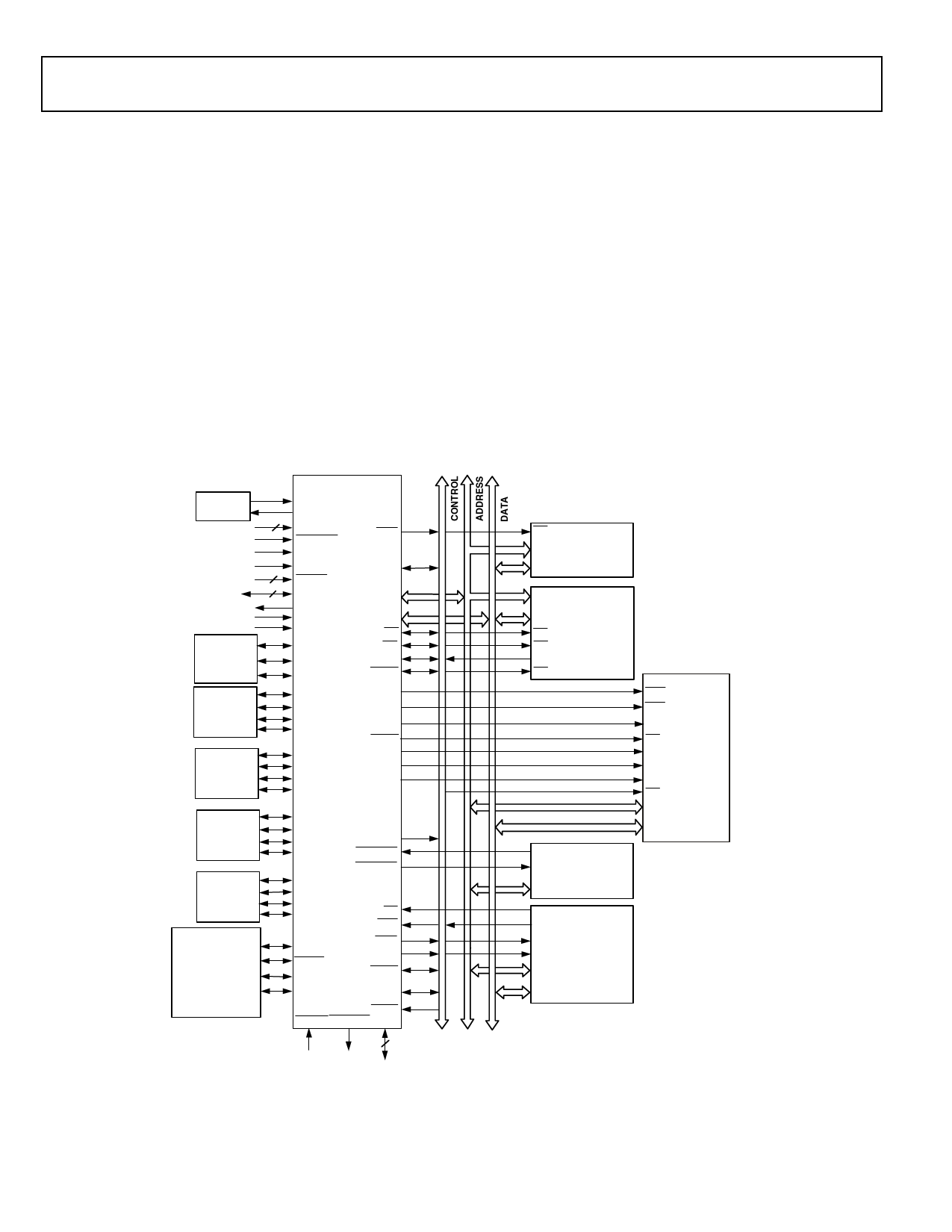

The ADSP-21161N continues SHARC’s industry-leading

standards of integration for DSPs, combining a high performance

32-bit DSP core with integrated, on-chip system features. These

features include a 1 M bit dual ported SRAM memory, host

processor interface, I/O processor that supports 14 DMA

channels, four serial ports, two link ports, SDRAM controller,

SPI interface, external parallel bus, and glueless multiprocessing.

The block diagram of the ADSP-21161N on Page 1 illustrates

the following architectural features:

• Two processing elements, each made up of an ALU, Mul-

tiplier, Shifter, and Data Register File

• Data Address Generators (DAG1, DAG2)

• Program sequencer with instruction cache

• PM and DM buses capable of supporting four 32-bit data

transfers between memory and the core every core

processor cycle

• Interval timer

• On-Chip SRAM (1 M bit)

• SDRAM Controller for glueless interface to SDRAMs

• External port that supports:

• Interfacing to off-chip memory peripherals

• Glueless multiprocessing support for six ADSP-

21161N SHARCs

• Host port read/write of IOP registers

• DMA controller

• Four serial ports

• Two link ports

• SPI compatible interface

• JTAG test access port

• 12 General-Purpose I/O Pins

Figure 1 shows a typical single-processor system. A multiprocess-

ing system appears in Figure 4 on Page 8.

CLOCK

2

3

12

LINK

DEVICES

(2 MAX)

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

ADSP-21161N

CLKIN

XTAL

CLK_CFG1-0

CLKDBL

EBOOT

LBOOT

IRQ2-0

BMS

BRST

FLAG11-0 ADDR23-0

TIMEXP

RPBA

ID2-0

DATA47-16

RD

LXCLK

WR

LXACK

LXDAT7-0

ACK

MS3-0

SCLK0

FS0

D0A

D0B

SCLK1

FS1

D1A

D1B

RAS

CAS

DQM

SDWE

SDCLK1-0

SDCKE

SDA10

SERIAL

DEVICE

(OPTIONAL)

SERIAL

DEVICE

(OPTIONAL)

SPI

COMPATIBLE

DEVICE

(HOST OR SLAVE)

(OPTIONAL)

SCLK2

FS2

D2A

D2B

SCLK3

FS3

D3A

D3B

CLKOUT

DMAR2-1

DMAG2-1

CS

HBR

SPICLK

SPIDS

MOSI

MISO

HBG

REDY

BR6-1

PA

SBTS

RESET RSTOUT JTAG

7

CS

ADDR

DATA

BOOT

EPROM

(OPTIONAL)

ADDR

DATA MEMORY

OE

AND

PERIPHERALS

WE (OPTIONAL)

ACK

CS

RAS

CAS SDRAM

DQM (OPTIONAL)

WE

CLK

CKE

A10

CS

ADDR

DATA

DMA DEVICE

(OPTIONAL)

DATA

HOST

PROCESSOR

INTERFACE

(OPTIONAL)

ADDR

DATA

Figure 1. System Diagram

–4–

REV. A