EVAL-CED1Z(Rev0) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

EVAL-CED1Z

(Rev.:Rev0)

(Rev.:Rev0)

EVAL-CED1Z Datasheet PDF : 32 Pages

| |||

AD7262

TIMING SPECIFICATIONS

AVCC = 4.75 V to 5.25 V, CA_CBVCC = CC_CDVCC = 2.7 V to 5.25 V, VREF = 2.5 V internal/external; TA = TMIN to TMAX, unless otherwise noted.1

Table 2.

Parameter

fSCLK

tCONVERT

tQUIET

Limit at TMIN, TMAX

2.7 V ≤ VDRIVE ≤ 3.6 V 4.75 V ≤ VDRIVE ≤ 5.25 V

200

200

40

40

32

32

20

20

19 × tSCLK

19 × tSCLK

475

475

950

950

13

13

t2

10

10

t3 3

15

15

t4

29

t5

15

t6

0.4 × tSCLK

t7

0.4 × tSCLK

t8

13

t9

13

23

13

0.4 × tSCLK

0.4 × tSCLK

13

13

t10

5

5

35

35

t11

2

2

t12

2

2

t13

3

3

t14

3

3

tPOWER-UP

240

240

15

15

Unit

kHz min

MHz max

MHz typ

MHz max

ns max

ns max

ns max

ns min

ns min

ns max

ns max

ns min

ns min

ns min

ns min

ns max

ns min

ns max

μs min

μs min

ns min

ns min

μs max

μs max

Description

AD72622

AD72622

AD7262-5

tSCLK = 1/fSCLK

AD7262

AD7262-5

Minimum time between end of serial read/bus relinquish

and next falling edge of CS

CS to SCLK setup time

Delay from 19th SCLK falling edge until DOUTA and DOUTB are

three-state disabled

Data access time after SCLK falling edge

SCLK to data valid hold time

SCLK high pulse width

SCLK low pulse width

CS rising edge to falling edge pulse width

CS rising edge to DOUTA, DOUTB, high impedance/bus

relinquish

SCLK falling edge to DOUTA, DOUTB, high impedance

SCLK falling edge to DOUTA, DOUTB, high impedance

Minimum CAL pin high time

Minimum time between the CAL pin high and the CS

falling edge

DIN setup time prior to SCLK falling edge

DIN hold time after SCLK falling edge

Internal reference, with a 1 μF decoupling capacitor

With an external reference, 10 μs typical

1 Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of AVCC) and timed from a voltage level of 1.6 V.

All timing specifications given are with a 25 pF load capacitance. With a load capacitance greater than this value, a digital buffer or latch must be used. See the

Terminology section.

2 See the Serial Interface section.

3 The time required for the output to cross 0.4 V or 2.4 V.

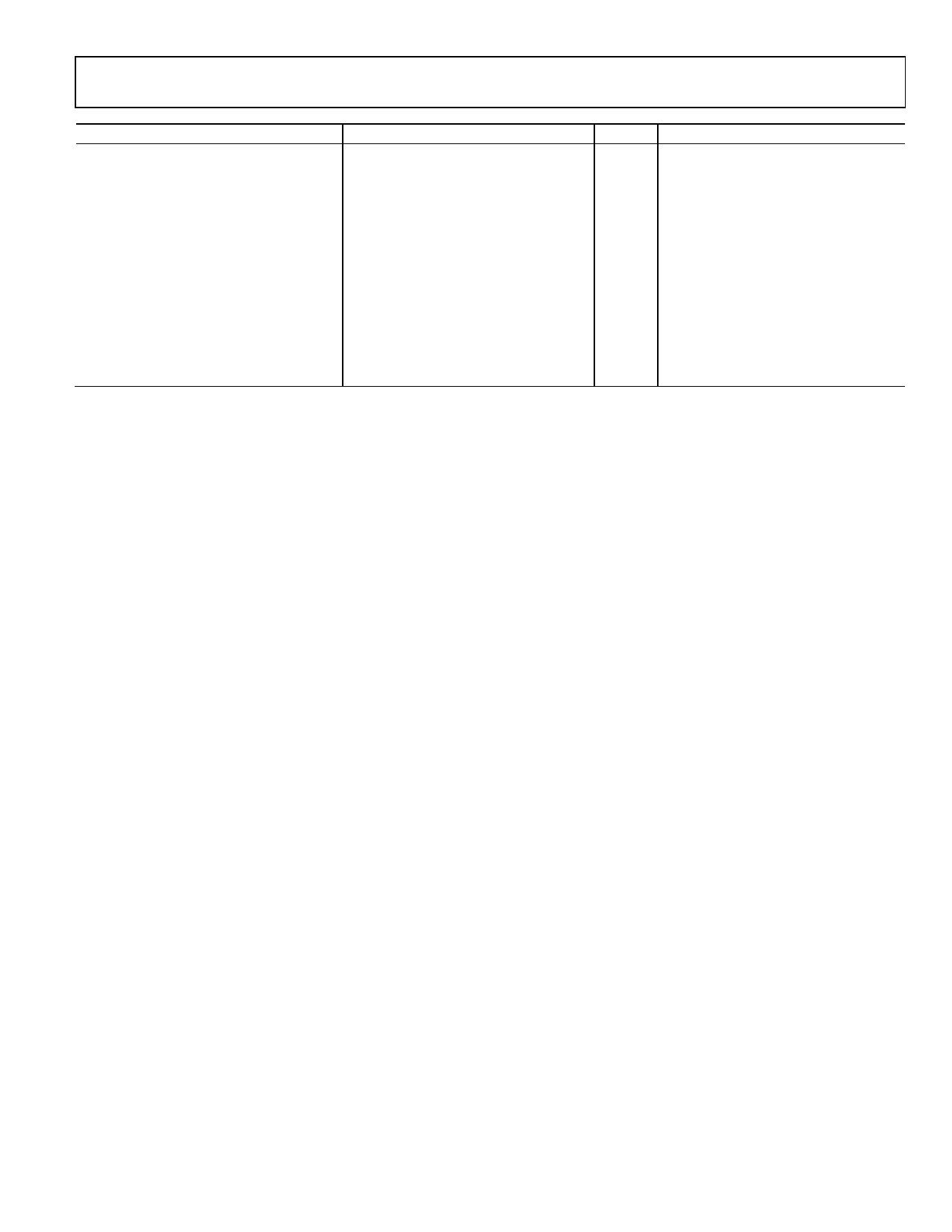

TIMING DIAGRAM

CS

SCLK

t2

1

2

3

4

DOUTA

DOUTB

THREE-STATE

THREE-STATE

t6

5

18

19

20

21

t3

t7

t4

t5

DB11A DB10A DB9A

DB11B DB10B DB9B

Figure 2. Serial Interface Timing Diagram

t8

29

30

31

t9

DB1A

DB0A

DB1B

DB0B

tQUIET

THREE-

STATE

THREE-

STATE

Rev. 0 | Page 6 of 32