AD679JNZ Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

AD679JNZ Datasheet PDF : 16 Pages

| |||

AD679

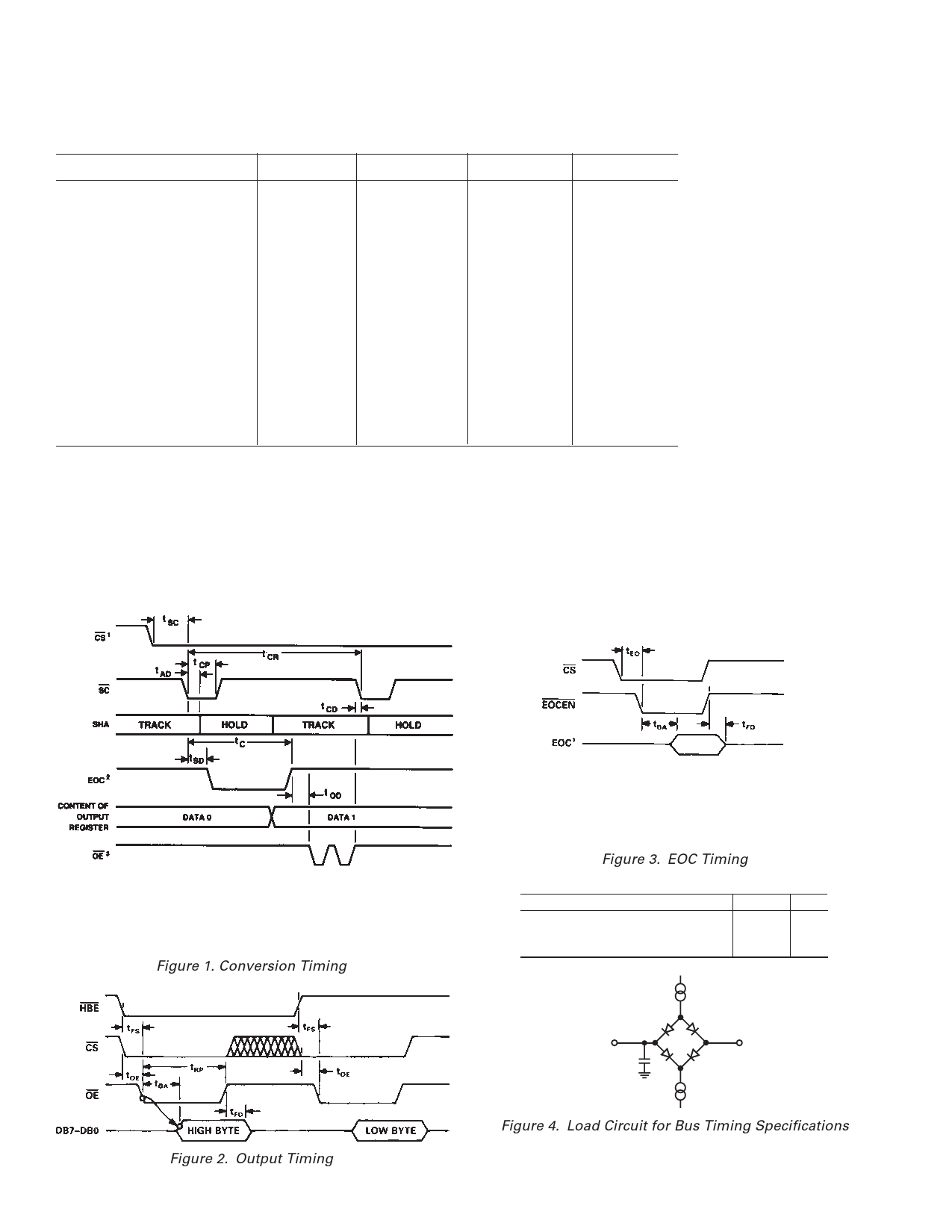

TIMING SPECIFICATIONS (All device types TMIN to TMAX, VCC = +12 V ؎ 5%, VEE = –12 V

؎ 5%, VDD = +5 V ؎ 10%)

Parameter

Symbol

Min

Max

Unit

SC Delay

Conversion Time

Conversion Rate1

Convert Pulse Width

Aperture Delay

Status Delay

Access Time2, 3

Float Delay5

Output Delay

Format Setup

OE Delay

Read Pulse Width

Conversion Delay

EOCEN Delay

tSC

50

ns

tC

6.3

µs

tCR

7.8

µs

tCP

0.097

3.0

µs

tAD

5

20

ns

tSD

0

400

ns

tBA

10

100

ns

10

574

ns

tFD

10

80

ns

tOD

0

ns

tFS

100

ns

tOE

20

ns

tRP

195

ns

tCD

400

ns

tEO

50

ns

NOTES

1Includes acquisition time.

2Measured from the falling edge of OE/EOCEN (0.8 V) to the time at which the

data lines/EOC cross 2.0 V or 0.8 V. See Figure 4.

3COUT = 100 pF.

4COUT = 50 pF.

5Measured from the rising edge of OE/EOCEN (2.0 V) to the time at which the output voltage changes by 0.5. See Figure 4; COUT

= 10 pF.

Specifications subject to change without notice.

NOTES

1IN ASYNCHRONOUS MODE, STATE OF CS DOES NOT AFFECT OPERATION.

SEE THE START CONVERSION TRUTH TABLE FOR DETAILS.

2EOCEN = LOW (SEE FIGURE 3). IN SYNCHRONOUS MODE, EOC IS A THREE-

STATE OUTPUT. IN ASYNCHRONOUS MODE, EOC IS AN OPEN DRAIN OUTPUT.

3DATA SHOULD NOT BE ENABLED DURING A CONVERSION.

Figure 1. Conversion Timing

NOTE

1EOC IS A THREE-STATE OUTPUT IN SYNCHRONOUS MODE

AND AN OPEN DRAIN OUTPUT IN ASYNCHRONOUS. ACCESS (tBA)

AND FLOAT (tFD) TIMING SPECIFICATIONS DO NOT APPLY IN

ASYNCHRONOUS MODE WHERE THEY ARE A FUNCTION OF THE

TIME CONSTANT FORMED BY THE 10pF OUTPUT CAPACITANCE

AND THE PULL-UP RESISTOR.

Figure 3. EOC Timing

TEST

ACCESS TIME HIGH Z TO LOGIC LOW 5V

FLOAT TIME LOGIC HIGH TO HIGH Z

ACCESS TIME HIGH Z TO LOGIC HIGH

FLOAT TIME LOGIC LOW TO HIGH Z

VCP

100pF

0V

0V

5V

COUT

10pF

100pF

10pF

IOL

Figure 2. Output Timing

DOUT

COUT

VCP

IOH

Figure 4. Load Circuit for Bus Timing Specifications

–4–

REV. D